- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- In STM32G4 TIM, I am confused: how can software ch...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

In STM32G4 TIM, I am confused: how can software choose bypass Dead-time generator?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 8:36 PM - edited 2023-10-24 10:17 PM

HI experts ,

May you have a nice day!

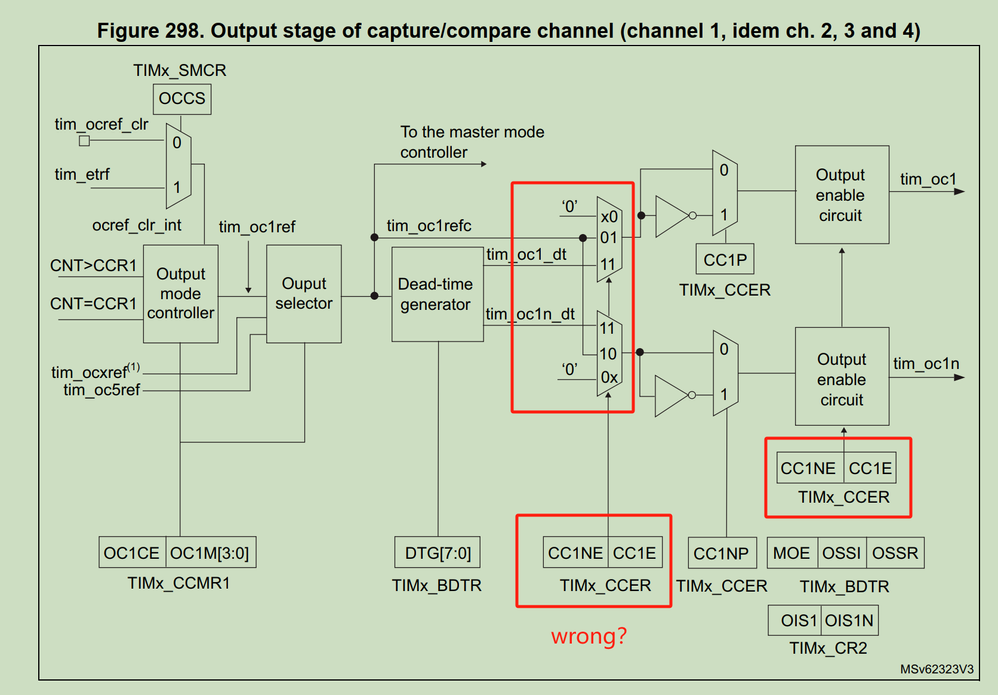

this figure is in rm0440-STM32G4 Series Reference manual. STM32F4, STM32F3 have the same TIM.

now I have some question:

1. how can I configure the Modules in the red box, such as selecting x0, 01 or 11?

2. I find CC1E and CC1NE can only enable the OC1 and OC1N output. WHY there are two function position(red box) for CC1E and CC1NE bit? is it something wrong?

Looking forward to hearing from the experts!

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-25 1:46 AM

CC1E and CC1NE are bits in TIMx_CCER, see description of that register in TIM chapter of RM.

The above picture illustrates the following facts:

- Dead time is generated only if both these bits are set.

- Also, if CCxNE is set (CH1N is enabled) and CCxE bit is cleared (CH1 is disabled), CH1N is not inverted.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-25 1:46 AM

CC1E and CC1NE are bits in TIMx_CCER, see description of that register in TIM chapter of RM.

The above picture illustrates the following facts:

- Dead time is generated only if both these bits are set.

- Also, if CCxNE is set (CH1N is enabled) and CCxE bit is cleared (CH1 is disabled), CH1N is not inverted.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-25 2:17 AM

thank you very much, this realy surprising!

- Can FreeRTOS software timer generate PWM? in STM32 MCUs Embedded software

- CubeMX 6.15.0 generates wrong HRTIM deadtime prescaler macros for STM32G474 in STM32CubeMX (MCUs)

- STM32CubeMX 6.17.0 released in STM32CubeMX (MCUs)

- Calibrating the STM32's real-time clock (RTC) in STM32 MCUs Products

- STM32F411RE (Nucleo) PWM TIM1_CH1 - PA8 appears shorted to 5V when powered, unaffected by BOOT0 or NRST. in STM32 MCUs Boards and hardware tools