- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- I'm using TIM6-DAC-DMAMUX-DMA to create a periodic...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

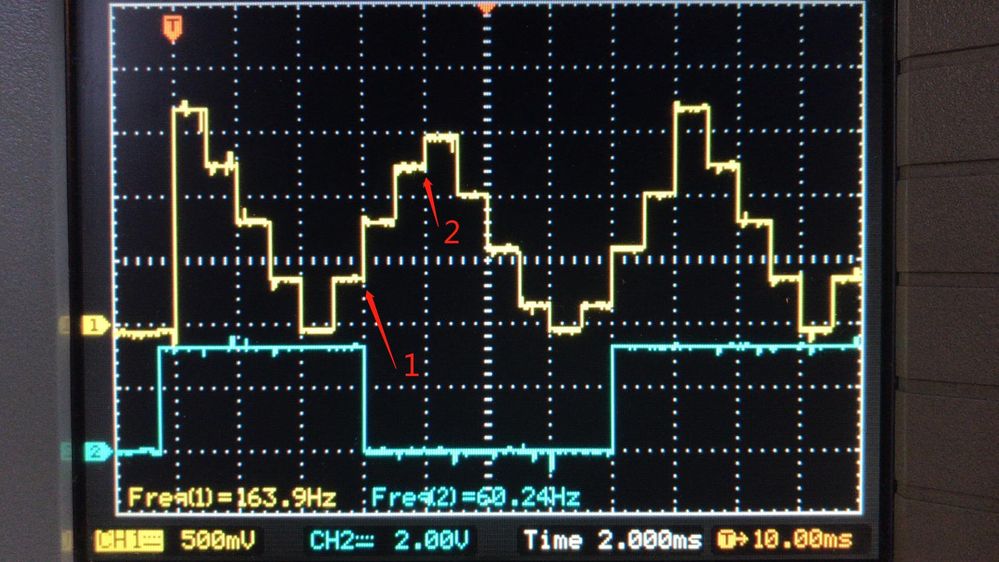

I'm using TIM6-DAC-DMAMUX-DMA to create a periodic signal as shown in the following picture. The yellow curve is DAC output, and green curve is a toggled GPIO for debug.

I catched an unexpected interrption time point which is described as followed:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-16 1:19 AM

Registers Setting:

DMA_S0CR: MSIZE=PSIZE=16bit, DBM=1, MINC=1, CIRC=1, DIR=M2P, TCIE=1, EN=1

DMA_S0NDTR = 8

DMA_S0M0AR points to a buffer: 0x8000, 0x6000, 0x4000, 0x2000, 0x0000, 0x2000, 0x4000, 0x6000

DMA_S0M1AR points to a buffer: 0x7000, 0x5000, 0x3000, 0x1000, 0x0000, 0x1000, 0x3000, 0x5000

When TCIF0 interruption occurs, I toggle the green GPIO to indicate transfer completed.

Trigger: TIM6 generates TRGO when EN and UPDATE.

I got an interrupt at time point 1(red arrow), Is this the time when DMA finished reading from memory? why doesn't it occur at the next trig ? (There are only 7 trigs from begining, not 8).

But, the important qestion is, how can I got the interrupt at time point 2 ?, because I think this time point is a right time to stop the DAC output when a full periodic signal has finished.

- Labels:

-

DAC

-

DMA

-

STM32H7 series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-17 8:24 AM

Read the DAC chapter - DMA writes to DHR register when it's empty, and it gets transferred to DOR register by the trigger (coming from timer).

At 1, what happened was, that a trigger arrived from timer, 0x4000 got transferred from DHR to DOR thus the output pin's level changed appropriately, DOR got empty, subsequenly DMA tranferred 0x6000 into DAC_DHR (where it remained until the next trigger), and as that was the 8th transfer, it threw the TC interrupt.

> But, the important qestion is, how can I got the interrupt at time point 2 ?

One way to achieve that would be to count to 8+1 (and subsequently to 8) in an interrupt triggered by the same timer which triggers the DAC.

JW

- Unexpected data corruption when camera and display both running (with SDRAM framebuffers in between) in STM32 MCUs Products

- CubeMX2: I2S Sample rate calculation does not match value computed in hardware by HAL in STM32CubeMX2 (MCUs)

- Unexpected Behavior of the STM32 CRYP Module in STM32 MCUs Security

- About OEMiROT_Appli_TrustZone for H563ZIT6 SBSFU in STM32 MCUs Security

- STM32C0 not driving CAN bus in STM32 MCUs Products