- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How to stop receiving UART data with DMA.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to stop receiving UART data with DMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-04 09:00 PM

Hi all

I'm triying using DMA to receive UART.

But the number of UART data is depending on the situation.

So I want to set a CNDTR register with margin.

I was wondering that I can stop DMA before CNDTR is zero.

When DMA Enable bit is cleared, it seem that don't stop immediately.

I think that the cause is that CNDTR is not zero.

But I want to stop DMA before CNDTR is zero.

Is there way to solve it?

Regards,

- Labels:

-

DMA

-

UART-USART

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-04 10:34 PM

Which STM32?

> When DMA Enable bit is cleared, it seem that don't stop immediately

Why do you think so?

It just finishes the last transaction if it already started.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-04 11:48 PM

>Which STM32?

I'm using Nucleo-G071RE.

CNDTR is set with margin(Because data size is not constant)

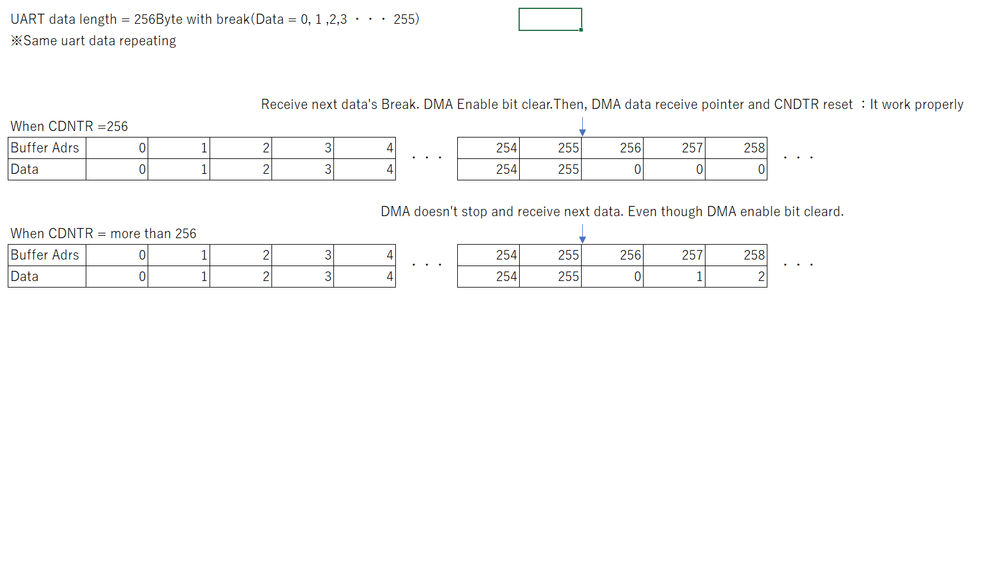

I took test by 256Bytes date with break(Break is mark of data starting).

And I coded that when I recieve break, DMA data receive pointer and CNDTR reset, then receive restart.

When I set 256Bytes to CNDTR, it worked properly.

When I set more than 256Byte to CNDTR, it does'nt work as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-05 08:57 PM

In your example, when it "works", the data becomes 0, 0, 0, ...

When it "doesn't work", the data is 0, 1, 2, ...

Since you're sending 0, 1, 2, ..., that statement seems backwards to me.

Writing EN=0 definitely disables the stream.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-05 10:49 PM

In this test situation, 1 packet is 256Bytes.

I programmed that when it received 256Bytes, then En = 0 , then data pointer set to "Buffer adr = 0" , CNDTR is reset(256 or more than 256), En = 1.

So, My expected result is that there is no data above "Buffer Adrs = 256".

I was wondering that result depending on CNDTR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-06 03:16 AM

Okay, that makes more sense.

It should work as you expect. When EN=0, the DMA is off. There's likely a bug in the code somewhere.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-06 06:10 AM

Thank for you replying.

I'll check my code again.

- Acoustic Echo Cancelling U5 in STM32 MCUs Embedded software

- STM32Cube IDE problem flashing the code in STM32CubeIDE (MCUs)

- STM32H747 USB with DMA does not work in STM32 MCUs Embedded software

- STM32H7 optimized SPI driver for use in DMA mode in STM32 MCUs Products

- STM32 USB Host CDC class: USBH_FindInterface issue in STM32 MCUs Products