How to generate three level pwm for power converters?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-22 6:36 PM

Hello everyone, I have medium level in stm32 mcu's like using adc's, timers and also HRTIM peripheral in 32f334 and G4 series but I can't figure out the optimum way to generate three level spwm waveforms for using with NPC inverter that I'm designing now. I searched a lot across the web and it's shame the such a great mcu like stm32 doesn't have a single example on how generate such a pwm scheme. Even the applications notes from st doesn't mention that and they don't provide source code for it like

"STDES-PFCBIDIR - 15 kW, three-phase, three-level converter". I prefer using hrtim as I'm familiar with. Thank you in advance

- Labels:

-

HRTIM

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-22 11:03 PM

What is three level PWM? Can you post sketch of the expected waveform?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-23 2:44 AM

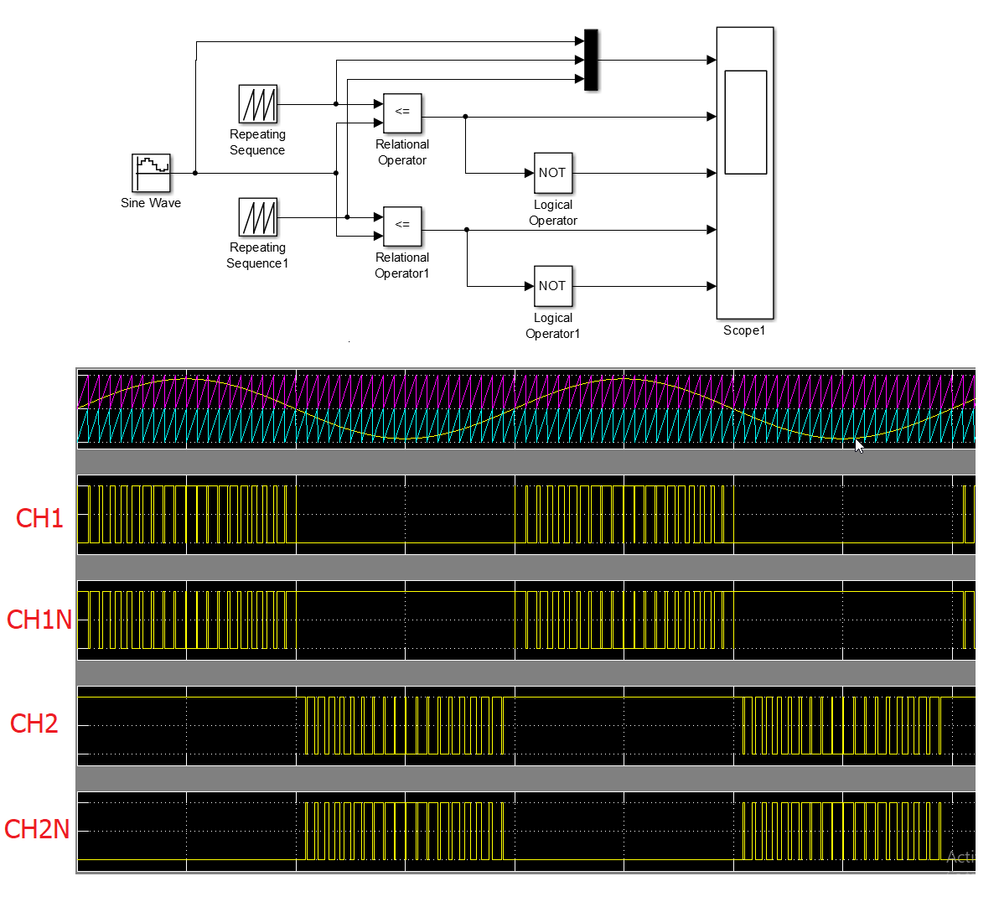

this is the concept block diagram and the required pwm waveforms

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-23 4:01 AM

How does this differ from any other cycle-by-cycle-controlled PWM?

You probably want to review the timer-DMA examples in Cube, where from a prepared table, related reghisters (CCRx) in timer are changed by DMA triggered from Update of the same timer, through the TIMx_DCR/TIMx_DMAR mechanism.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-23 4:13 AM

Now I know I have to use two output compare (and complementary) units, The problem when I use hrtim, comparing very low and very high values results an unpredictable behavior (the minimum compare value is not 0 and the max compare value is not TIM_PERIOD).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-23 4:15 AM

The difference is I have to compare the sinewave to two sawtooth signals, not one like the traditional pwm

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-23 4:29 AM

> The difference is I have to compare the sinewave to two sawtooth signals, not one like the traditional pwm

Well, that just means using two channels, as you've remarked above. The difference in the table-DMA-driven approach is then, that DMA does not feed one channel but two, that's why using the DCR/DMAR mechanism.

I am not familiar with the detailed working of HRTIM.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-23 4:46 AM

> I am not familiar with the detailed working of HRTIM.

The A-F timing units in HRTIM each have its individual DMA trigger/channel so they can simply work out of two tables determining their individual output waveforms.

For the "idle" state, I'd try to use the fact that

A compare value greater than the period register value will not generate a compare match event.

in which case only the set/reset assigned to Period would be active.

JW