How to generate Center Aligned PWM with variable duty cycle that has PWM frequency of 1.5MHz with dead time insertion?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-06 6:51 AM

Hello,

I need to be able to generate a center aligned PWM signal on two Ch. with 1.5MHz PWM frequency. The duty cycle variation will have dead time inserted in it. In order to generate 1.5MHz for center aligned signals, I need to calculate ARR Register for 3 MHz PWM frequency.

I am currently exploring this with Nucleo-F446RE bare metal programming. I selected PLL of 84MHz Timer Clock Frequency. But still, I am not able to get good precision / resolution in the PWM duty cycle and the signals looks skewed as well due to such high PWM frequency.

Is there any other chip family more suitable for such application? What's the best method to be able to generate such PWM signal and get good control over duty cycle variation?

Thank you.

- Labels:

-

STM32F4 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-06 2:07 PM

Post content of time registers and oscilloscope/LA screenshots with describing/drawing how the signal fails short of expectations.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-06 4:52 PM

With 84 MHz clock and a 3 MHz timer update frequency, you're going to have fairly grainy resolution. No way around that.

The STM32H7 can have a 480 MHz timer clock for HRTIM. That'll increase resolution. As jan notes, you'll need to figure out what is acceptable for your application. Hard to know what "good" and "signals looks skewed" means to you without any other explanation or pictures.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-07 12:38 AM

Switch to 180 MHz on some APB2 timer. That will give 60 PWM width divisions with center aligned mode and 120 divisions with basic PWM mode.

STM32G4 also has HRTIM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-07 6:07 AM

Thank you all for your responses...

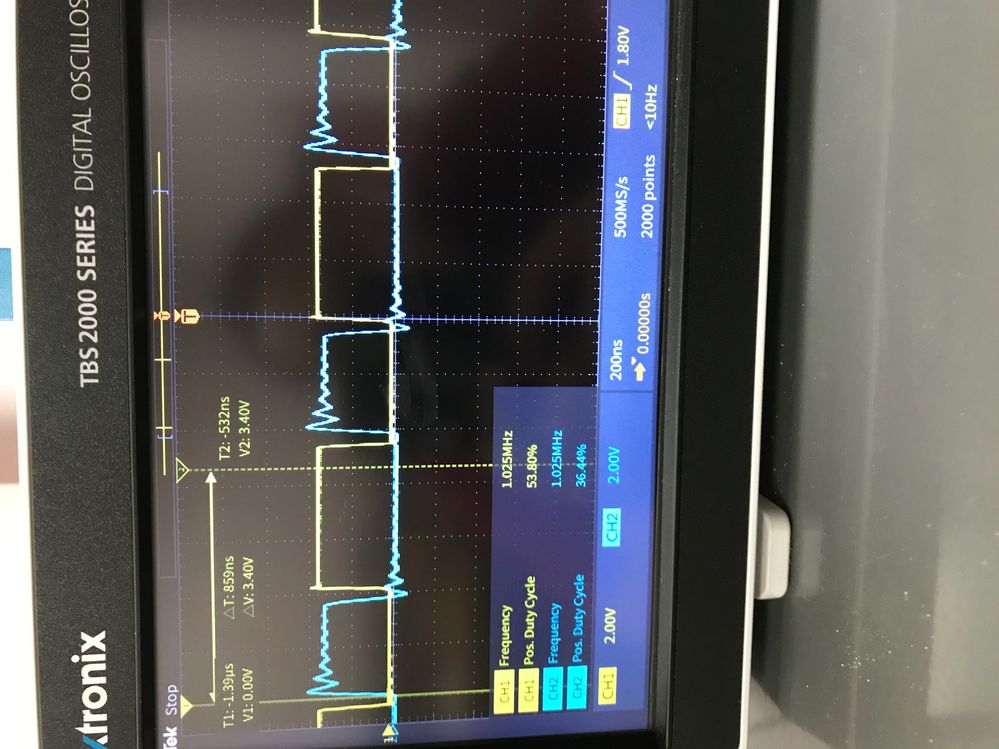

I've the screenshot of the signals attached from the scope. As it can be seen, the signals are skewed due to the slew rate and high PWM frequency.

With the parameters as below, I am able to generate 1 MHz PWM signals with some dead period insertion. Again, I don't think the shape / skewed signals would be of any problem in the application. My main concern is limited resolution available in PWM duty cycle variation with some dead period insertion.

I am still exploring the dead period (DTG) and Clock Division factors in CR1 registers to check all available configurations.

void TIM8_PWM_Setup (void)

{

RCC->APB2ENR |= RCC_APB2ENR_TIM8EN;

TIM8->PSC = 1 - 1;

TIM8->ARR = 42 - 1; //to be able to generate 1 MHz Center aligned PWM

TIM8->CNT = 0;

TIM8->CCR1 = ((DutyCycle_Counter * 10 * 42) / 100) - 1;

TIM8->CCMR1 &= ~0xFFFF;

TIM8->CCMR1 |= 0x0060;

TIM8->CCER &= ~0xFFFF;

TIM8->CCER |= (TIM_CCER_CC1NE | TIM_CCER_CC1E);

TIM8->BDTR |= (TIM_BDTR_MOE | TIM_BDTR_DTG_1);

TIM8->CR1 |= 0x120;

TIM8->CR1 |= TIM_CR1_CEN;

}

SYSCLK and APB2 Timer Clock: 84 MHz.

(Maximum APB2 Clock available is only 90 MHz; and not 180 MHz with STM32F446RE).

Please advise for any corrections / improvements in the code parameters to optimize the duty cycle resolution in PWM..

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-08 1:09 PM

> (Maximum APB2 Clock available is only 90 MHz; and not 180 MHz with STM32F446RE).

Yes, but timer clock is twice the respective APB clock, if APB divider is >1.

Slew rate of signal edges is given by GPIO_OSPEEDR setting.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-08 2:36 PM

To reduce ringing probably try to enable the compensation cell also. Read RM0390 section 8.1 and look for SYSCFG_CMPCR register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-20 10:08 AM

thank you all, for your reply..