- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How to calculate ADDSET and DATAST according ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to calculate ADDSET and DATAST according to SRAM timing graph?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-04-27 12:38 AM - edited 2023-11-20 06:59 AM

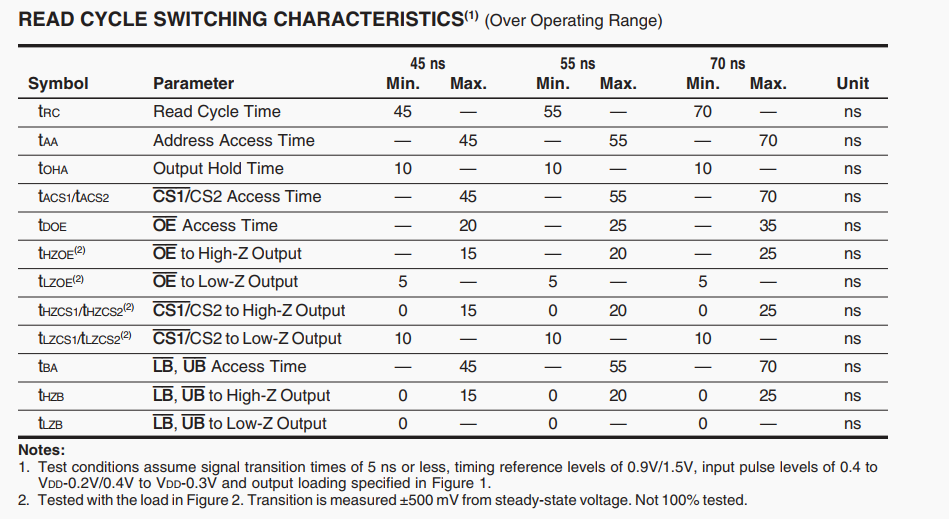

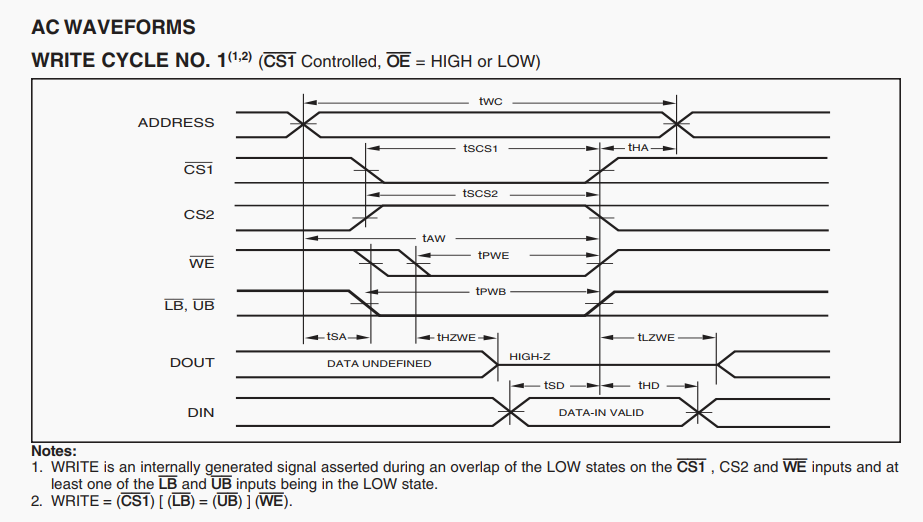

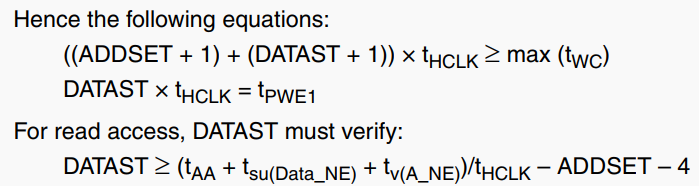

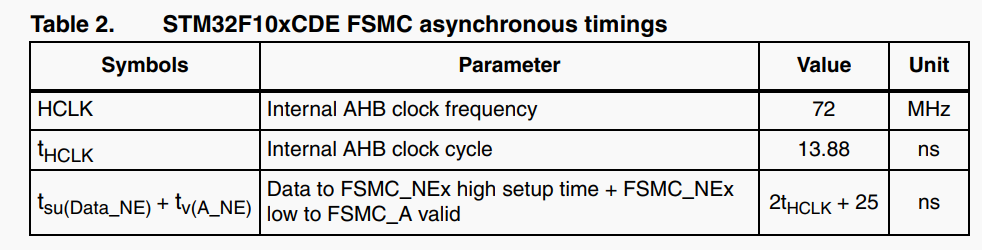

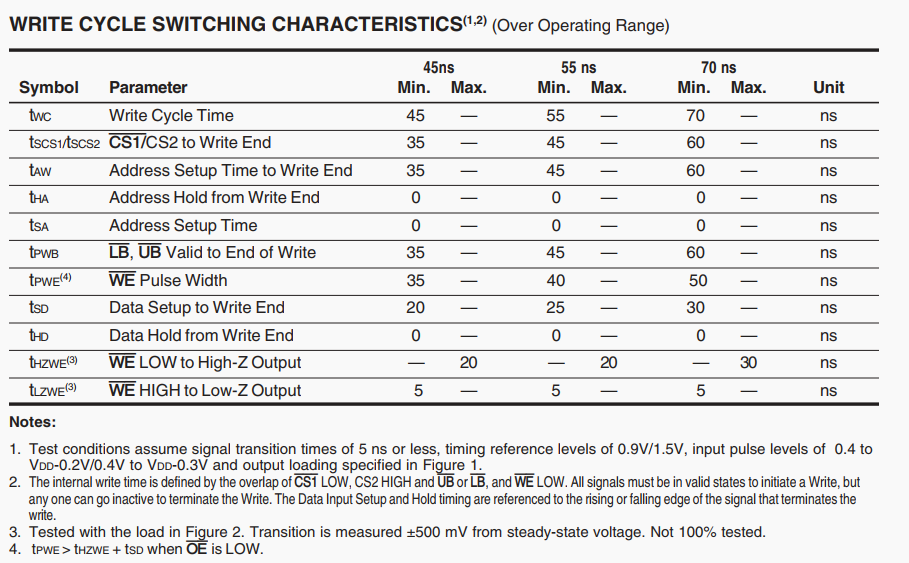

I use FSMC in STM32F407 to access external SRAM IS62WV51216. I read RM0090 and AN2784, gives me two fomula

tSU means

- why WE have two falling edges on the left

- what dose tSU tV mean,where is it in the timing graph please draw it. My ENglish is not good and I have some issues on reading, don`t understand "Data to FSMC_NEx high low to FSMC_A valid setup time + FSMC_NEx".It is conflict.

- Where is ADDSET and DATAST in STM32 parallal in SRAM timing graph, how to calculate ADDSET and DATAST, I really nead your help.

- Labels:

-

FMC-FSMC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-04-27 06:40 PM

@A ST Supporter @Abdelaziz GOULAHSEN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-03 06:19 PM

@Tilen Majerle

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-03 06:19 PM

@Majerle

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-05-03 07:27 PM

@Community member @andrewg @Majerle

- Write to TIMx break and dead-time register in STM32 MCUs Embedded software

- ILI9163v on stm32 in STM32CubeIDE (MCUs)

- PWM center aligned to half-period of TIM in STM32 MCUs Products

- Calculate ARR value for Timer TIM2, TIM3 in STM32F407 in STM32 MCUs Products

- maximum baudrate on uart in half-duplex mode in STM32 MCUs Products