- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How timers in STM32F7 start workig?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How timers in STM32F7 start workig?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-28 03:41 AM

While preparing slides for students about timers in STM32F7 microcontrollers, I came across several inaccuracies in the description of their work presented in the STM32F7 reference manual RM0410 rev 4. The following sentence can be found in the mentioned document: “Note that the actual counter enable signal CNT_EN is set 1 clock cycle after CEN�?. However, in Fig 337 one of the signal is signed as follows (CEN=CNT_EN), which contradicts the statement from the quoted sentence.

In turn, elsewhere in the same document I came across the following sentence: “As soon as the CEN bit is written to 1, the prescaler is clocked by the internal clock CK_INT�?. How should I understand the statement "as soon as" – in the same moment? Fig. 337 shows that the signal CK_PSC appears two periods of CK_INT after the rising edge of CNT_EN. However, in Figs. 331 to 333 I see something different – the signal CK_PSC exists before the rising edge of CNT_EN.

- Labels:

-

Documentation

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-09 07:09 AM

Hello,

I agree there are several errors in these figures. The internal clock and CK_PSC (before the prescaler) are existing before the rising edge of CNT_CEN.

On the figure 337, on must remove the "CK_CNT=CK_PSC" as well as CEN= CNT_CEN.

The counter clock CK_CNT always appear after the CEN bit write.

Another error: the clock actually appears 2 cycles after CEN write (Fig. 337 is correct for this, while Fig. 331, 335, 336 are wrong).

This will be corrected for the next timer specifications revision, and deployed for next reference manuals releases.

Best regards,

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-09 11:38 AM

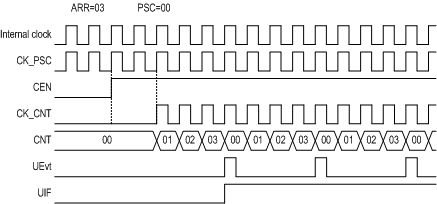

Thank you for your reply. I have prepared a drawing that takes into account your answer. Please correct me if something is wrong.

I steel do not know what is the relation between the CEN bit and the CNT_EN signal. Is it set 1 clock cycle after CEN bit?

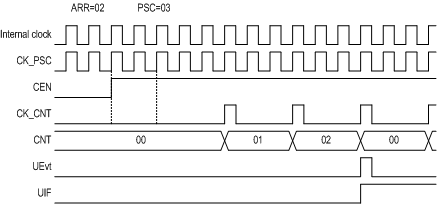

I also don't know how the counter starts when the PSC is different from 0. For this case I have also prepared a drawing. If it is incorrect, I would be grateful if you could point out any errors in it.

Best regards,

Mirek

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-10 08:02 AM

Hello Mirek,

The 2 drawings are perfect.

The CNT_EN (counter enable) signal is set 2 cycles after CEN bit write. But you better not mention this, it doesn't bring much to the understanding of the timer, and it is even confusing. It is enough to see the ck_cnt starting 2 cycles after CEN.

Best regards,

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-20 07:56 PM

Hi, Vincent,

I just posted a post asking for the same question. Then got member told me this was discussed last year. So I searched in the forum and came to this post.

Just to clarify, in that case, for the statement "Note that the actual counter enable signal CNT_EN is set 1 clock cycle after CEN" it is still valid, is it?

From CEN to CNT_EN there is 1 clock cycle, then due to prescalor is 0, the CK_CNT is the same frequency as the CK_INT. But for CK_CNT, the clock appears 1 prescaled cycle after the CNT_EN. That explains the 2 clock cycles here in the Figure 120 (The figure is from RM0008 Reference Manual). Is that right?

Also, another stupid question, CEN, DIR and UG are bits in different registers. Then what about CK_INIT, CNT_EN, what are these signals?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-22 04:38 AM

Hi, Mirek,

I also came to this problem in RM0008 manual (released in Dec 2018 comparing to Mar 2018 of the one you used), which leads me to your post by searching online.

This is my understanding version of this problem. It says "Note that the actual counter enable signal CNT_EN is set 1 clock cycle after CEN"

So CNT_EN should be 1 clock cycle after CEN bit. Meanwhile, it seems that from CNT_EN, the count will start counting from the original value in the counter register, so the CK_CNT will start 1 prescaled cycle from the CNT_EN trigger.

Therefore, when PSC=00, it shows as 2 clock cycles from CEN to CK_CNT.

When PSC=03 as you set in your 2nd figure, I think that is wrong. The frequency is divided by (PSC+1). So if PSC=03, then the CK_CNT frequency should be divided by 4 (your one is divided by 3). I suppose that is wrong. And based on my aforementioned understanding, from CEN to CNT_EN 1 clock cycle, then to CK_CNT first rising edge should be 1+(PSC+1)=5 clock cycles, which is correct in your case.

- Master TIMER3 -> Slave TIMER1 Synchronization: Slave Timer ETR pulse counting in STM32 MCUs Products

- Nucleo-F767ZI MX_Device_HID example regeneration has multiple failures in STM32CubeMX (MCUs)

- How to initialise timer for 1.25ms interrupt in stm32f7 ..provide example in STM32 MCUs Embedded software

- Using an Aliexpress STM32G070RBT6 board, no ST-Link in STM32 MCUs Boards and hardware tools

- STM32F767/77 controller power consumption ? in STM32 MCUs Products