- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How PLL affects timer Pre-sclaer.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How PLL affects timer Pre-sclaer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 03:23 AM

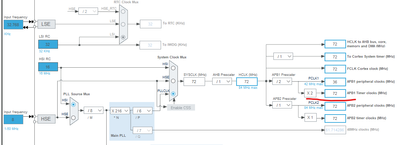

Below i have attached a code which enables the PLL freq of 72MHz using HSI of 16MHz. The issue is if I give a Timer pre-scaler of 36000-1 (I am using timer2, which in case of STM32F401RE is on APB1 bus so using a pre-scaler of 2 for APB1 which makes it 36MHz, thus a pre-scaler of 36000-1 will generate a delay of 1 ms). Desired outcome is to generate 1 ms timer delay but it is not 1 ms when tested with timer ARR is set 5000. I have already checked clock using MCO1 pin with a pre-scaler of 2 which gave 36MHz on DSO. When i call a delay function by passing 5000 as timer ARR value, then i hardly get 2500 - 3000 ms delay.

Below is my RCC_Init() function, please let me know is there any other settings are needed for setting up timers using PLL.

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-26 01:37 AM

As the TIM clock is 72MHz and you can't set PSC to 72000-1 (as it's only 16-bit), set it to 36000-1 and multiply value to be written to ARR by 2 (and don't forget to subtract 1).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 03:28 AM - edited 2023-08-25 03:30 AM

Hello @DJ1 ,

Have you tried using STM32CubeMX?

I suggest you to use STM32CubeMX , It helps you for the configuration of the STM32 peripherals and Clock configuration.

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 05:34 AM

I tried using CubeMx, but only for PLL config. In my code that is fine, but when i try to generate a delay of lets say for eg 1ms i get output of only 981 microseconds. Due to this mismatch i think entire delay is changing. Can it be due to HSI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 06:20 AM

> when i try to generate a delay of lets say for eg 1ms i get output of only 981 microseconds

> Can it be due to HSI.

Yes, absolutely. You're seeing an error of 1.9%. Let's check the datasheet for the HSI:

So it guarantees ±1% at ambient before part is soldered. Soldering will change that some. You can adjust the HSI using HSITRIM to get it more accurate.

If you need good accuracy, crystal+HSE is going to be much more accurate.

Also be aware ARR is preloaded and there's probably better ways to do delays, but that is a side issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 02:08 PM

If you use APB prescaler other than 1, timer clock is 2x APB clock.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 09:31 PM - edited 2023-08-25 09:32 PM

Exactly, but the thing is if i kept APB1 pre-scaler as /2 (72MHz / 2 = 36 MHz) then APB1 timer clock should be 2*APB clock (still 72MHz), now if i want to generate a precise blocking delay of 1 ms than what shall be my Timer pre-scaler settings.

Below i have mentioned once again:

{

TIM2->TIMx_ARR = x;

TIM2->TIMx_CNT = 0;

TIM2->TIMx_CR1 |= (1 << 0);

while(TIM2->TIMx_CNT < (x));

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-25 09:46 PM

I understand the clock issue with HSI but as of now i am trying to test my system later we can switch the PLL input clock. As described, the issue lies when i try to test a blocking delay function, whose settings are

Pre-scaler : 36000 and ARR is based on the user passes a value to a function. The thing is the timer is generating exactly half the time delay than expected. For eg: if i set 5 secs i get delay of 2.5sec. I think issue lies with Pre-scaling only. For that reason i set the TIMPRE bit in RCC_DCKCFGR register but no effect.

What can be the solution for this, as if i am setting a timer interrupt for every 1ms and increment a variable uptill 5000 then everything is fine but i fell thats not the solution

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-26 01:37 AM

As the TIM clock is 72MHz and you can't set PSC to 72000-1 (as it's only 16-bit), set it to 36000-1 and multiply value to be written to ARR by 2 (and don't forget to subtract 1).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-26 01:40 AM

> For that reason i set the TIMPRE bit in RCC_DCKCFGR register but no effect.

If APB divider is 2, TIM clock is the same in either of RCC_DCKCFGR.TIMPRE setting. Read RCC_DCKCFGR.TIMPRE description in RM.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-26 01:45 AM - edited 2023-08-26 02:13 AM

True, but in CubeMX settings i can see APB1 clock settings different as well as Timer clock settings on that bus different

Thanks, the solution worked for me, but can you explain what does APB1 Timer clocks and APB1 peripheral clocks mean, like how are they different.

- Bug in TIM_Base_SetConfig, fix TIM_Base_SetConfig to block first interrupt in STM32 MCUs Embedded software

- Can PWM settings affect other timer settings? in STM32 MCUs Products

- PWM generation at very low Duty-cycle in STM32 MCUs Products

- LPUART interrupt occur not immediately cause overrun with FreeRTOS tickless. in STM32 MCUs Products

- About STM32F429 DAC in STM32 MCUs Products