- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- HAL_QSPI_AutoPolling() fail when polling the SR of...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

HAL_QSPI_AutoPolling() fail when polling the SR of NOR flash in QPI mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-28 06:03 AM

Hi,

I'm using STM32H750B with a NOR flash (Winbond's W25128 chip). When the chip is configured as QPI mode. If polling SR1 using the auto polling function, it will throw error. But read SR directly and check the bits works.

Any help? Thanks.

Solved! Go to Solution.

- Labels:

-

QSPI

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-10 07:25 AM

I confirm that W25Q128JV-DTR supports QPI mode.

Can you try your indirect mode configuration (4-4-4) and add 1 or 2 Dummy-cycles ? for example: qspi_cmd->DummyCycles = 2;

Then, please keep me informed about your progress on this.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-28 08:08 AM

Hello @diverger ,

Please share your QUADSPI configuration to help you resolve your issue.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-29 07:19 PM

The pseudo code is as below:

// Send ERASE_SECTOR_CMD

send(ERASE_SECTOR_CMD);

// Auto Polling

qspi_cmd->InstructionMode = QSPI_INSTRUCTION_4_LINES;

qspi_cmd->Instruction = 0x05;

qspi_cmd->AddressMode = QSPI_ADDRESS_NONE;

qspi_cmd->AddressSize = QSPI_ALTERNATE_BYTES_24_BITS;

qspi_cmd->AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

qspi_cmd->AlternateBytes = 0;

qspi_cmd->AlternateBytesSize = 0;

qspi_cmd->DummyCycles = 0;

qspi_cmd->DataMode = QSPI_DATA_4_LINES;

qspi_cmd->DdrMode = QSPI_DDR_MODE_DISABLE;

qspi_cmd->DdrHoldHalfCycle = QSPI_DDR_HHC_ANALOG_DELAY;

qspi_cmd->SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

qspi_cmd->Address = 0;

qspi_cmd->NbData = 0;

qspi_poll->Match = 0x00;

qspi_poll->Mask = 0x01;

qspi_poll->MatchMode = QSPI_MATCH_MODE_AND;

qspi_poll->StatusBytesSize = 1;

qspi_poll->Interval = 0x16;

qspi_poll->AutomaticStop = QSPI_AUTOMATIC_STOP_ENABLE;

HAL_QSPI_AutoPolling(qspi_hdl, qspi_cmd, qspi_poll, timeout_ms);

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-04 03:00 AM

Hi @diverger ,

I see you are trying to use QUAD 4-4-4 mode, memories that support this mode require to enable it.

Are you sure that the memory support the Quad mode ? If yes, did you correctly enable it ? Please share the exact memory part number.

Can you please test the following configuration:

qspi_cmd->InstructionMode = QSPI_INSTRUCTION_1_LINE;

qspi_cmd->Instruction = 0x05;

qspi_cmd->AddressMode = QSPI_ADDRESS_NONE;

qspi_cmd->AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

qspi_cmd->DummyCycles = 0;

qspi_cmd->DataMode = QSPI_DATA_1_LINE;

qspi_cmd->DdrMode = QSPI_DDR_MODE_DISABLE;

qspi_cmd->DdrHoldHalfCycle = QSPI_DDR_HHC_ANALOG_DELAY;

qspi_cmd->SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

qspi_poll->Match = 0x00;

qspi_poll->Mask = 0x01;

qspi_poll->MatchMode = QSPI_MATCH_MODE_AND;

qspi_poll->StatusBytesSize = 1;

qspi_poll->Interval = 0x10;

qspi_poll->AutomaticStop = QSPI_AUTOMATIC_STOP_ENABLE;

HAL_QSPI_AutoPolling(qspi_hdl, qspi_cmd, qspi_poll, timeout_ms);Then, please keep me informed about your progress on this issue.

I also advise you to have a look at this AN4760: Quad-SPI interface on STM32 microcontrollers and microprocessors, this will help you on the Quad-SPI interface and configuration.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-05 06:04 AM

Yes, I'm sure I've enabled the QPI mode. And I can use normal read and check (in QPI mode) the status, and it works well. But it seems the auto-polling function won't work in this mode. My chip is w25q128jv.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-08 01:20 AM

Hi @diverger ,

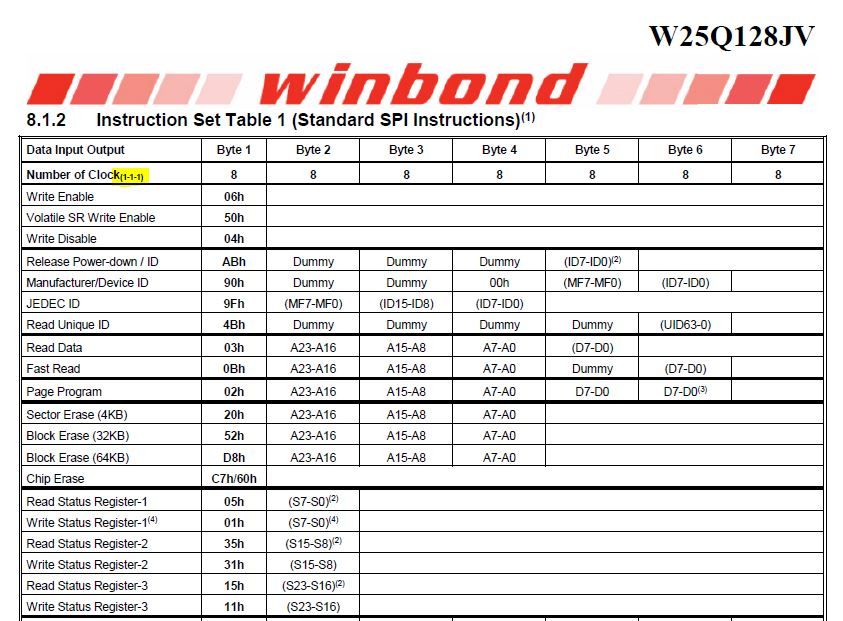

I found different info that you may want to check: according to the W25Q128JV datasheet, the read status register is only in standard SPI mode (1-1-1).

For more details, please check the W25Q128JV datahseet , in sections:

- 8.1.2 Instruction Set Table 1 (Standard SPI Instructions)

- 8.1.3 Instruction Set Table 2 (Dual/Quad SPI Instructions)

- 8.2.4 Read Status Register-1 (05h), Status Register-2 (35h) & Status Register-3 (15h)

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-10 05:44 AM

Hi @Imen DAHMEN Thanks for your patience.

Actually I'm not very sure if my chip is W25Q128JV or W25Q128JV-DTR (the chip is on a EVAL-board, and I need ask for the BOM to get the exact part number), the latter one apparently supports this command in QPI mode. And I can read the JESD SFDP table, it shows it support DTR, so my chip is very likely the latter one. And another evidence is, I can read back the status register in QPI mode (using 4-4-4 line pattern) indeed. As you know, auto-polling is just making the read-and-check more 'auto', they use same command.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-10 07:25 AM

I confirm that W25Q128JV-DTR supports QPI mode.

Can you try your indirect mode configuration (4-4-4) and add 1 or 2 Dummy-cycles ? for example: qspi_cmd->DummyCycles = 2;

Then, please keep me informed about your progress on this.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-12 12:02 AM

Hi, @Imen DAHMEN

I tried two cases:

- As you have recommended, adding 2 dummy waiting clocks will work. Both 0 and 1 waiting clocks won't work.

- After sending the erase command, wait some time, then auto polling the SR will work too.

Any conclusion? Are there some reasons related with timing or clock frequency?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-12 12:54 AM

Hi @diverger,

I'm glad to know that your issue is solved

In order to assure enough “turn-around�? time for changing the data signals from output mode to input mode, there must be at least one dummy cycle when using dual or quad mode to receive data from the Flash memory.

So, the QSPI require to insert two dummy-cycle in order to read correctly in quad mode, and this will not impact the read transfer from the status register.

The memory will always output the status register since it's clocked.

Imen

Thanks

Imen

- STM32H7 HW CS unexpected set inactive during SPI transfer in STM32 MCUs Products

- STM32F401 ADC VrefInt and Vbat read issue in STM32 MCUs Products

- stm32g0b0ce flash page erase issue in STM32 MCUs Products

- STM32G030 and X-CUBE-EEPROM in STM32 MCUs Embedded software

- Interrupt Not Triggering for External Buttons on STM32H7S78-DK in STM32 MCUs Products