- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: GPIO rise/fall time on Nucleo H7

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

GPIO rise/fall time on Nucleo H7

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-17 02:03 PM

I am prototyping an application on a Nucleo H7 board and I would like to use 50 MHz SPI master for performance reasons.

At lower speeds (25 MHz, for example) I am able to generate a fairly clean SPI Mclk that passes requirements, however at 50 MHz I end up with a clock signal that very much resembles a sine wave and does not meet setup / hold requirements.

I have tried various configurations of the SPI peripherals (e.g., 100 MHz master clock /2 divider, 200 MHz master clock /4 divider), various master clock sources, etc. At this point I am fairly sure that the problem I am observing is related to the GPIO characteristics of the Mclk pin.

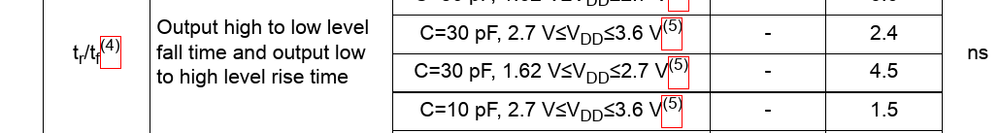

Referencing "Table 68. Output timing characteristics" of the datasheet "Output high to low level fall time and output low to high level rise time" =~ 5ns (depends on load capacitance) @ very fast drive speed, I would expect to see a better signal here, one that reaches 3.3V (or 1.8V - I tested both!) and levels off for some time before falling edge @ 50 MHz. But obviously I don't see that.

So my questions are:

- Am I interpreting Table 68 correctly, is it realistic to generate a nice looking 50 MHz clock from an H7 GPIO?

- Are there some characteristics of the Nucleo board in particular (very high load capacitance?) that might make things worse?

Thank you.

Solved! Go to Solution.

- Labels:

-

GPIO-EXTI

-

SPI

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-17 02:22 PM

How are you looking at the signals?

With a scope using a 10X probe?

The SPEEDR settings in the GPIO controls the slew-rate, you should try to find the appropriate speed/load setting

On the H7 there's also an IO Compensation cell, this should be enabled in SystemClock_Config()

On the NUCLEO, check the schematic and traces. Check that the pins you're using don't have stubs or other paths / components on them.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-17 02:22 PM

How are you looking at the signals?

With a scope using a 10X probe?

The SPEEDR settings in the GPIO controls the slew-rate, you should try to find the appropriate speed/load setting

On the H7 there's also an IO Compensation cell, this should be enabled in SystemClock_Config()

On the NUCLEO, check the schematic and traces. Check that the pins you're using don't have stubs or other paths / components on them.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-17 02:28 PM

(2) Yes, if you connect SPI device to the Nucleo with flying wires - no chance for 50 MHz.

The best I could get with such setup was maybe 5 MHz.

On a real board the same SPI device works at ~ 30 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-18 01:49 AM

the pins are fast, here from H743 data:

to see 50MHz square, need fast scope and probe - what you use here ?

see

https://community.st.com/s/question/0D53W00001vpp0NSAQ/can-make-a-50mhz-pwm-output

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-21 10:56 AM

When your question is answered, please mark this topic as answered by choosing Select as Best for the preferred answer, as also explained here. This will help other users find that answer faster.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-22 01:31 PM

Thanks for the replies everyone. I was able to resolve the issue, two items were in need of correction:

- My scope probe had a long path to ground, shortening it cleaned up the signals dramatically and allowed me to observe the effect of changing SPEEDR settings + IO compensation.

- MCLK was already set to "very fast" SPEEDR (this is the default in the stm SDK when SPI alternate function is selected), setting MOSI and MISO to "very fast" allowed transfer to work successfully @ 50 MHz.

I did not change (or need to change) IO compensation regs and I was not able to find sufficient documentation about how / when to use it.

I will select Mr. DeLorean's answer as "Best", but the other two answers were helpful as well. Thank you to all.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-22 03:14 PM

People are using external Ethernet PHY boards with RMII interface, which works exactly at 50 MHz. Most likely the typical issues are with the ground loops.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-22 07:50 PM

Point taken, 10x. But ethernet has a different kind of signaling, not returning to zero? also, it is more resistant to data errors.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-23 01:55 PM

RMII is a CMOS level logical interface from the MAC/MCU to PHY, not the physical 100BASE-TX modulated triple-level signal, which comes after the PHY.

- STM32L476, HAL library SPI3 write lead to hard reset in STM32 MCUs Boards and hardware tools

- SBSFU: encountering unexpected TLV error in STM32 MCUs Security

- Program doesn't work anymore after ST-Link upgrade in STM32 MCUs Products

- While Running Motor Starts Jerking. in STM32 MCUs Motor control

- Write to TIMx break and dead-time register in STM32 MCUs Embedded software