- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Generate a specific PWM signal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Generate a specific PWM signal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-18 01:01 AM - edited 2023-10-23 02:03 AM

Hi ST community,

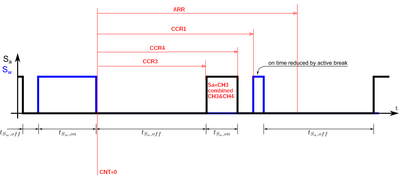

For a project I would like to generate two interdependent PWM signals (Sa and Sw in the attached figure) with the STM32G0. The constraints/tasks are as follows:

- tSw,off = constant for ~100ns

- tSw,on = in a time range from ~100ns to 20us and is limited cycle by cycle by an active break (peak control application).

- tSa,off = set every 300us in a time range from ~100ns to 30us.

- tSa,on = is set every 300us in a time range from ~100ns to 5us.

The times for tSa,off and tSa,on are thus adjusted every 300us. The time tSw,on is limited cycle by cycle by the active break.

Following limitations I had to mention:

- I'm allowed to interrupt the software all 300us for a few us (so polling could be difficult).

- Focus on the STM32G0 microcontroller series.

- The on time tSw,on is limited cycle by cycle with an comparator.

I will not present my previous approaches now, in order not to influence your ideas.

I look forward to your feedback.

Br, Stefan

Solved! Go to Solution.

- Labels:

-

STM32G0 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-23 01:58 AM

I tried the "Combined PWM" (without "DMA burst") and found that the "Preload" functions (ARR preload and CCR preload) work (in contrast to the operation in "One Pulse Mode").

Next I will try to connect the COMP output to the ETR and thus end the phase Ts,w prematurely. However, I am concerned that the time tSa,off will be extended, which would not be acceptable for the final application.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-23 08:53 AM

> However, I am concerned that the time tSa,off will be extended

It won't if you do what I said above.

(Also I never said One Pulse Mode and I don't see how and why would that be applicable here.)

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-23 10:52 PM - edited 2023-10-23 10:53 PM

(Also I never said One Pulse Mode and I don't see how and why would that be applicable here.)

This is true, in the past we have often used the OPM to run similar projects (cycle by cycle peak controlled applications).

I tired to follow your instructions and implement this code after I started the combined PWM:

TIM1->AF1 |= TIM1_AF1_ETRSEL_0; // SET COMP1 output as ETR input source

TIM1->SMCR |= 0x70; // Set Bit 4,5 and 6 to ue ETR as trigger input

TIM1->SMCR |= 0x4; // Set slave mode selection (SMS) to Reset mode

In the attached screenshot you can see the first small signal measurements. In yellow (C1) the output of TIM1 channel 1, in blue (C3) the output of TIM1 channel 3 and in green the output of the COMP1. As you can see, the comparator output limits the on time of TIM1 channel 1 (as expected) and it looks like that the CNT is also reset in this case (because of the missing TIM1 channel 3), which is also somehow expected, because in the RM0444 the SMS description mentions this for the Reset mode. But this is not an option for the final application. As shown in the picture of the first post, after a limited tSw,on the defined tSa,off should occur. Any hints to improve this?

Thx & Br

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 01:24 AM - edited 2023-10-24 01:44 AM

Post content of TIM1 registers.

Which channel is which signal?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 01:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 02:02 AM

> Regarding channel - signal link:

No, I mean, which one is Sa and which one is Sw?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 02:06 AM

- TIM1.CH1 (yellow) Sw ("breaked" by the COMP_OUT(green))

- TIM1.CH3 (blue) Sa

Br, Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 02:23 AM

What I said above was:

> Timer period starts at beginning of Tsa,off. Tsa,on generated using Combined PWM mode as TDK said above. Tsw,on normally generated using the plain PWM2 mode on one channel, as timer period ends with end of Tsw,on.

So, if TIM1.CH3 is Sa, it should be generated by combined mode from CCR3 and CCR4, thus those should be the shorter two values; CCR1 should be biggest of the three (there's no need for CH1 = Sw to be in Combined mode, and I said that above too).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 02:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-24 04:08 AM

Based on your drawing, I tried to implement both signals within the combined PWM.

- Sw: TIM_CH1 = CCR1 & CCR2 (where CCR2 = ARR)

- Sa: TIM_CH2 = CCR3 & CCR4

The ETR configuration remains the same.

In the software I update the registers every 300us. As you can see in the figure below, the tSa,off (orange) graph changes as expected without unexpected jumps (NICE).

I also tried to simulate a break situation of the tSw,on. The comparator output limits the on-time of TIM_CH1 as expected without changing tSw,on or other timings.

But if I understand you correctly, your idea was to run the Sa with the combined PWM function and the Sw with the PWM2 mode. I have tried this and it works as well. Why do you prefer this approach? Because with this approach one register less has to be written?

Thanks & Br

Stefan

- Floating outputs when not connected to PWM Timer 8 in STM32 MCUs Products

- Debug Issue with STM32H7B3I-DK and TouchGFX 4.24.2 in STM32CubeIDE 1.17.0 in STM32 MCUs TouchGFX and GUI

- While(1) Not Executing in STM32 MCUs Products

- Timer 1 Retriggerable One-Pulse Mode in STM32 MCUs Products

- PWM Capture with EXTI Interrupts: Eliminating Noise Spikes in STM32 MCUs Products