- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- FMC: How to delay chip select?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FMC: How to delay chip select?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-25 1:41 AM

I should combine STM32F479 with PROFIBUS-DP ASIC SCP4-2

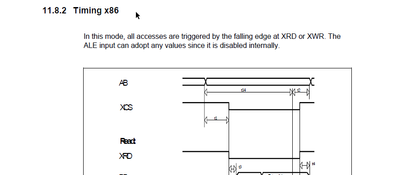

The chip is aged. And requires delay of at least 30ns (by 3v3) between address and cs. Our previous design was based on SAM4S and their CPUs are offerring register to program such delays. In STM32F4 reference all the pictures suggesting that cs is always phase synchronous to AB change.

Did I overlooked something? How to deal with this?

- Labels:

-

FMC-FSMC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-25 3:28 AM

The STM32 FMC is far from being perfect with regard to flexibility of provided signals, their polarities and timing. It is what it is.

So here, you won't be able to get away without external glue logic.

You can try to delay the CS signal e.g. using a shift register clocked from the system clock. Maybe a scheme could be devised where the NEx is fed into a timer's channel which would provide the delay; but this would need some more thought.

Or maybe Mode D could be employed, with a couple of gates combining NADV and NEx into the required chipselect waveform.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-25 3:50 AM

What about simply using another GPIO as CS?

Okay, DMA mode will be problematic...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-28 10:17 AM

Hi @AlexKern

The forum moderator had marked your post as needing a little more investigation and direct support. An online support case has been created on your behalf, please stand by for just a moment and you will hear from us.

Regards,

Billy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-29 2:18 AM

Hi @Billy OWEN ,

Please discuss this - and other topics opened in public forum - publicly, for benefit of both us and ST.

JW

- stm32g070rb ST-Link troubleshooting in STM32 MCUs Boards and hardware tools

- SPI Comminication between two microcontrollers in STM32 MCUs Embedded software

- Standard CubeMX project ICACHE error handler (STiRot + Secure Application) in STM32 MCUs Security

- Debugging NAND flash system infinitely hanging in STM32 MCUs Embedded software

- STM32F469 + AS4C4M16SA SDRAM – Read Returns Last Value with MSB Duplication Issue in Others: STM32 MCUs related