- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Does STM32H7xx SPI driver support adding delay...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does STM32H7xx SPI driver support adding delay between SCK and SS signals?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-31 03:07 AM

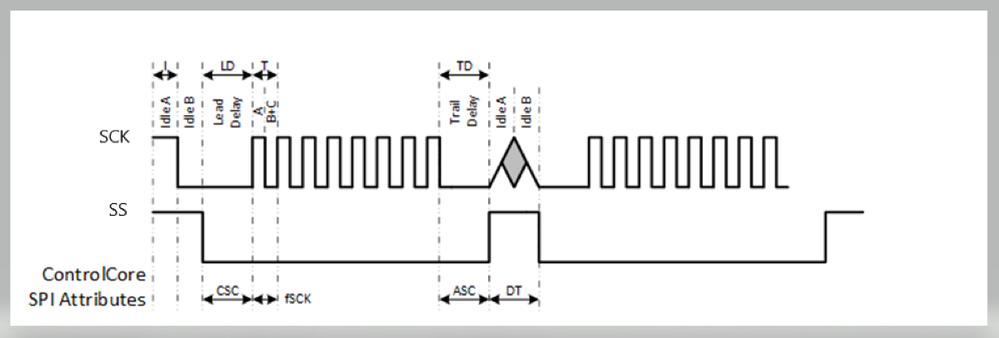

Usually peripherial SPI drivers support 3 delays to control signals timing:

- Delay from SS enable edge to first SCK edge (SS Idleness) - supported in STM32H7xx

- Delay between data (Inter-data Idleness)- supported in STM32H7xx

- Delay after SCK edge to SS disable edge (ASC in the picture) - seems to be not supported.

Does STM32H7 SPI support the third delay?

If not then, what is the value of it and does it depend on anything?

Can it be modified directly or indirectly by a different attribute?

Solved! Go to Solution.

- Labels:

-

SPI

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-31 08:17 AM

The third delay is not programmable, it is fixed to one SCK period.

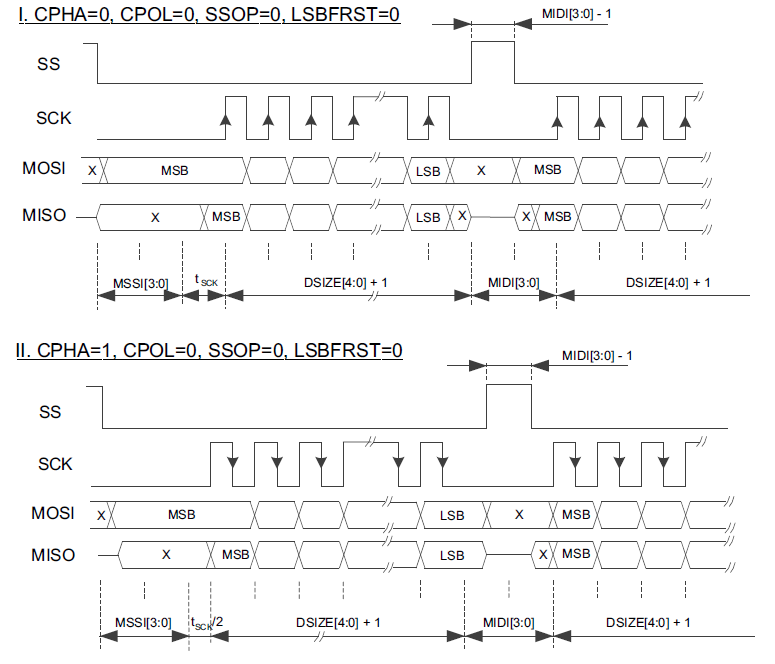

As you can see from the timing diagram below (extracted from the STM32H7 reference manual), in "Motorola" mode the SS signal goes inactive one SCK period after the last active edge of SCK (rising or falling depending on the CPHA and CPOL bits in the SPI_CFG2 register) and stays inactive for one less SCK period than the inter-frame gap specified in SPI_CFG2.MIDI[3:0].

Figure 775. SS interleaving pulses between data (SSOE=1, SSOM=1,SSM=0)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-31 06:14 AM

The SPI module in the 'H7 is overcomplicated, but not that much as you'd expect, see the SPI chapter in RM. It simply inserts a SS pulse of SPI_CFG2.MSSI lenght between frames, and RM/DS are not clear about its exact positioning.

If you want more precise control, you may want to generate SCK+SS e.g. using a timer, and loop it back externally to SPI set as slave.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-31 08:17 AM

The third delay is not programmable, it is fixed to one SCK period.

As you can see from the timing diagram below (extracted from the STM32H7 reference manual), in "Motorola" mode the SS signal goes inactive one SCK period after the last active edge of SCK (rising or falling depending on the CPHA and CPOL bits in the SPI_CFG2 register) and stays inactive for one less SCK period than the inter-frame gap specified in SPI_CFG2.MIDI[3:0].

Figure 775. SS interleaving pulses between data (SSOE=1, SSOM=1,SSM=0)

- Synchronize DMA to GPIO transfer on 2 distant MCU by external signal. in STM32 MCUs Products

- Can a STM32L496RG read a 20-bit SSI signal with a SPI interface? in STM32 MCUs Products

- Unable to Connect to Target STM32F412CEU6 in STM32 MCUs Products

- STM32H743xI/G, STM32H753xI device errata and ST HAL implementation? in STM32 MCUs Embedded software

- Problem with DAC+DMA End-of-Transmission Interrupts on STM32L452RET6P in STM32 MCUs Products