- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Does HAL_QSPI_AutoPolling respect Dual Flash ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does HAL_QSPI_AutoPolling respect Dual Flash Mode configuration?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-10 02:08 AM

Hi,

I have an application of which uses the STM32F469NI with two MX25L12833F QSPI flash in dual flash mode and are encountering an issue when using HAL_QSPI_AutoPolling().

CLK is configured at 1MHz (to allow for logic analyser), both devices share the same CLK and nCS lines, where nCS is provided from BK2_nCS.

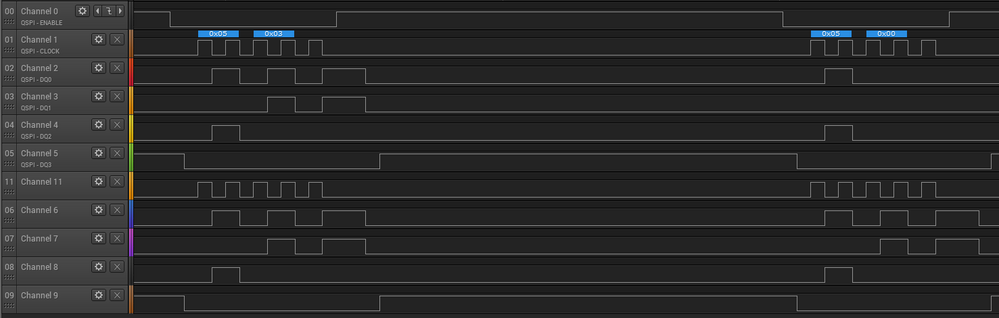

When performing a sector erase, the instruction is sent to both chips as outlined in AN4760 section 2.2.4, the peripheral is then configured to auto poll for the WEL and WIP bits to be reset. I am seeing that it does not respect both chips. The device on QSPI1 can finish and the autopoll stops yet the device on QSPI2 continues the erase operation. See attached snippet from a logic analyser where device 1 is CH2-5 and device 2 is CH6-9.

Is this expected behaviour or is extra configuration required for autopolling when using Dual Flash mode?

Thanks,

Jack

Solved! Go to Solution.

- Labels:

-

QSPI

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-10 03:00 AM

The byte request length should be set to two, and the match/mask as 16 bits wide where the status bits are put in both high and low bytes.

Have dual configuration here where mass erase in first chip a lot quicker than second, so the 2 bytes read, mask, compare forces both to be considered.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-10 03:00 AM

The byte request length should be set to two, and the match/mask as 16 bits wide where the status bits are put in both high and low bytes.

Have dual configuration here where mass erase in first chip a lot quicker than second, so the 2 bytes read, mask, compare forces both to be considered.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-10 07:45 AM

Thankyou very much! That has sorted it, unfortunately that isn't too clear from what is otherwise excellent documentation!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-10 08:19 AM

The common command and interleaving of bytes takes some getting ones head around, especially when reading/writing multiple registers.

Some of this could perhaps have been better rolled into the QUADSPI library code, as from the outset it configures the interface in dual mode.

Up vote any posts that you find helpful, it shows what's working..

- STM32G0 minimum ADC frequency in STM32CubeMX (MCUs)

- SPI communication issue on STM32F103RB (sort of buffer over/underun) in STM32 MCUs Embedded software

- STM32H745 EMC Behaviour internal Power in STM32 MCUs Boards and hardware tools

- Regarding VOL voltage at various IOL currents in STM32 MCUs Products

- Interrupt behavior and its priority in STM32CubeIDE (MCUs)