- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: connect AD converter 7903 with SPI from STM32F...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

connect AD converter 7903 with SPI from STM32F4

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-11-02 1:55 PM

Hello,

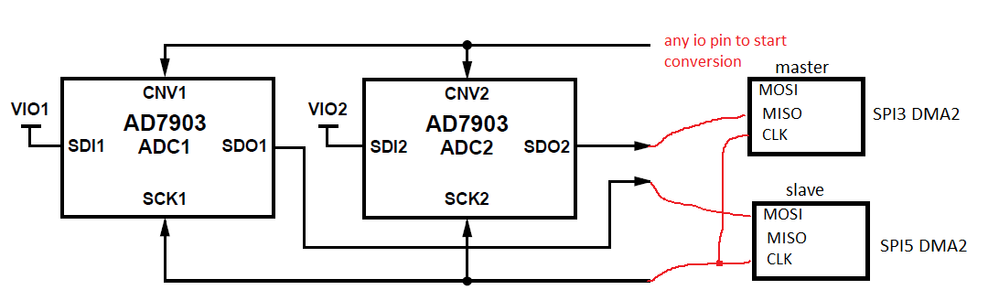

I want to connect an AD converter AD7903 with the STM32F429 http://www.analog.com/static/imported-files/data_sheets/AD7903.pdf The AD7903 can be driven in a simultaneous sampling mode. It is show in the datasheet on page 25. 1. Im not sure, if I have connect the AD7903 in the right way. I want to connect it, like in the picture. Is that ok, or must I split the clk conduct in CLK from SPI1 and CLK from SPI2? But then I have the problem, that is not be simultaneous. 2. I dont use the MOSI pins. Can I use them as a normaly pin, if I not activate the alternative function of this pin. 3. The maximum datarate of the AD7903 is 1MSPS. Is the STM32F429 with SPI fast enough? I have estimate if f_PCLK = 84MHz and I use a divider of 2, than I get a clock frequency of 42MHz. If I transmit 16Bit I get 42MHz/16 = 2,625 MSPS. Is that ok? 4. Is it possible to get samples of the STM32F429ZIT6 ? I have try it, but I get the answer, that I can buy it by xyv distributor. Thank you very much, for your help in advance Best regards Dirk #ad7903-spi-stm32f429- Labels:

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-11-03 6:13 AM

If you want them to work synchronously, then perhaps you can daisy-chain them and shift the data out as two 16-bit words?

Unless you are a business user of the parts, and have direct sales/support contacts, then yes it's probably cheaper and more efficient to buy your parts directly from the likes of DigiKey or Mouser, or RS/Farnell, or whomever that is in your locality.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-11-03 6:39 AM

Use one SPI as master and the other as slave, feeding the clock from the master to slave.

> I dont use the MOSI pins. Can I use them as a normaly pin, if I not activate the alternative function of this pin. Yes. > The maximum datarate of the AD7903 is 1MSPS. Is the STM32F429 with SPI fast enough? > I have estimate if f_PCLK = 84MHz and I use a divider of 2, than I get a clock frequency of > 42MHz. If I transmit 16Bit I get 42MHz/16 = 2,625 MSPS. Is that ok? I did not read the datasheet of AD7903, but if the sample/conversion time overlaps the shift out, then yes. However, count on the inflexibility of the SPI clock scheme - you have no other choice than fPCLK/2^N (N=1..8). Also, not all SPI are on the faster APB2 bus. Also, you will need to process the read data, and you have only some 160 cycles per the couple of samples - whether that is sufficient depends on your particular application. JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-11-03 8:49 AM

Hello,

thank you very much for answering my questions. Best regards Dirk- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-12-04 10:20 AM

Hello,

I have connected the AD7903 with the STM32F4 in the following way: I want to use a clock speed of 21MHz, because the SPI interface in slave mode has a maximum clock speed of 21MHz. Otherwise I would choose 42MHz. I want to continuously save the data from the AD converter with a clock frequency of 21MHz. I use the DMA2 controller, but I dont know, if this is fast enough to save the data in memory. 1. Can I get problems with the clock speed of 21MHz? 2. Assuming, I would use a clock speed of 42MHz. The same question like under point 1, can I get problems to save the data fast enough? 3. Is it better to split them into DMA controller 1 and DMA controller 2 ? 4. If I use SPI3 and SPI5 both in master mode and ADC1 is to SPI3 and ADC2 is connected to SPI5. Then I have two separate clock wires. Is the clock frequency synchronuos? No, or? Thank you in advance. Best regards, Dirk

________________

Attachments : AD7903_SPI3.png : https://st--c.eu10.content.force.com/sfc/dist/version/download/?oid=00Db0000000YtG6&ids=0680X000006I01b&d=%2Fa%2F0X0000000bSy%2Fcx35IOyNau3NwlR_9YCLM2F2Q5SnvmV8z5on9ChmgNU&asPdf=false

I want to use a clock speed of 21MHz, because the SPI interface in slave mode has a maximum clock speed of 21MHz. Otherwise I would choose 42MHz. I want to continuously save the data from the AD converter with a clock frequency of 21MHz. I use the DMA2 controller, but I dont know, if this is fast enough to save the data in memory. 1. Can I get problems with the clock speed of 21MHz? 2. Assuming, I would use a clock speed of 42MHz. The same question like under point 1, can I get problems to save the data fast enough? 3. Is it better to split them into DMA controller 1 and DMA controller 2 ? 4. If I use SPI3 and SPI5 both in master mode and ADC1 is to SPI3 and ADC2 is connected to SPI5. Then I have two separate clock wires. Is the clock frequency synchronuos? No, or? Thank you in advance. Best regards, Dirk

________________

Attachments : AD7903_SPI3.png : https://st--c.eu10.content.force.com/sfc/dist/version/download/?oid=00Db0000000YtG6&ids=0680X000006I01b&d=%2Fa%2F0X0000000bSy%2Fcx35IOyNau3NwlR_9YCLM2F2Q5SnvmV8z5on9ChmgNU&asPdf=false

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-12-04 11:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-12-05 8:36 AM

You'll have to own your development and experimentation tasks. Your going to have to do these thing to know what is/is not viable for your application.

Yes, suspect 21 MHz would be fine. Short wiring, appropriate grounding and signal paths. DMA, don't see that being an issue the data rate is 1/8 or 1/16 of the bit clocking rate, so bandwidth to memory should be adequate. Transfer enough data so you won't saturate interrupts. ie have a packet length of 100 bytes, use HT/TC DMA interrupts to manage a circular ping/pong operation. Two masters, yes the signals will be synchronous, but probably not in-phase with each other. The master/slave configuration looks to have the best potential, though you'll need to pump the master TX DMA, no experience here with Rx only configuration in that regard.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2015-02-12 11:08 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2015-02-13 8:32 AM

Did you actually get this to work, I'm facing a similar problem with dual ADC's

And what to this point have you actually tried to prototype/test in terms of topology?Up vote any posts that you find helpful, it shows what's working..

- Bootloader UART Issue – STM32G070CBT6 (DFU Works, but No Response via UART) in STM32 MCUs Embedded software

- Not Receiving UART message from STM32WL5M to Laptop in STM32 MCUs Wireless

- How to test STM32 MCU SPI communication using Host PC ? in STM32 MCUs Products

- Simple Upload Firmware By Customer using dapboot in STM32 MCUs Embedded software

- H750B Discovery FDCAN working when in loopback but not in standard mode in STM32 MCUs Embedded software