- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Chip Select of SPI in Nucleo F401RE stocked to...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Chip Select of SPI in Nucleo F401RE stuck low

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 5:17 AM - last edited on 2024-09-18 8:24 AM by Andrew Neil

Hi guys,

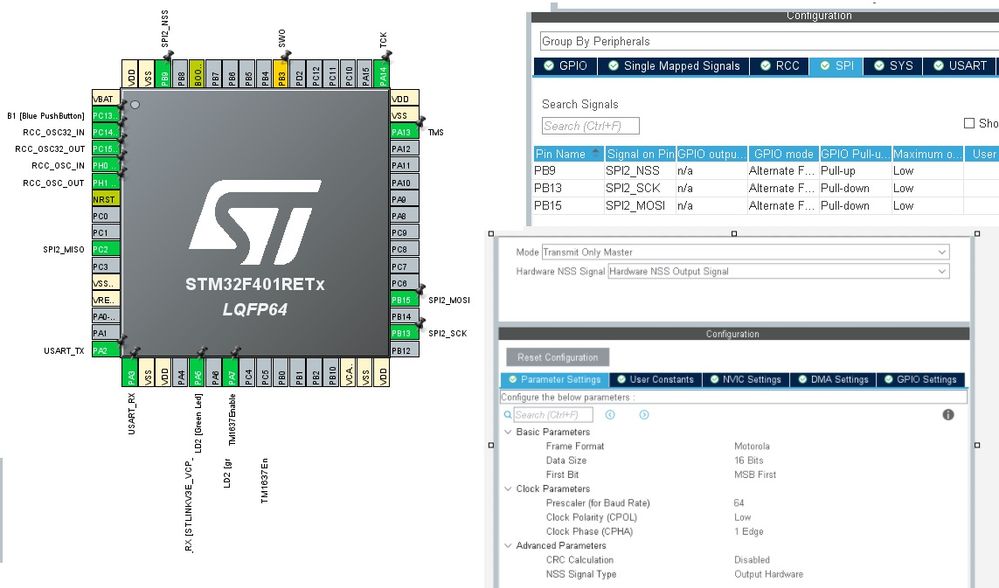

I m having an issue with my Nucleo F401RE. I m porting a code based on the use of SPI2 that worked very well on Nucleo G431RB. I made same setting on Nucleo IDE (see picture).

After inizialization of periperhals NSS (Chip Select) goes to high and everithing seems to work fine until the first transmission:

void SPI_TX_16b(uint8_t* pdata){

HAL_SPI_Transmit(&hspi2, (uint8_t*) pdata, 1, HAL_MAX_DELAY);

};

Then the NSS goes down and stucked there forever. In the picture (yellow is clk, green is data out, and violet is nss).

Any ideas?

Thanks

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 6:25 AM

Don't use the hardware NSS pin on the STM32F4, it's not driven like a CS pin. It will always be low when the peripheral is active. Instead, initialize it as a GPIO output and manually set it low before transmission, and high afterwards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 6:25 AM

Don't use the hardware NSS pin on the STM32F4, it's not driven like a CS pin. It will always be low when the peripheral is active. Instead, initialize it as a GPIO output and manually set it low before transmission, and high afterwards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 7:17 AM

ok fine.

But why the IDE mentions "hardware NSS output signal" if Chip select is not automatically managed? In G431RB used to work automatically

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 7:21 AM - edited 2024-09-18 7:21 AM

Different chips have different SPI peripherals and they behave differently. This is how it behaves on the STM32F4.

Why? Who knows, but newer chips behave differently so it feels like they recognized the issue. Just what it is. Keeping CS low is sometimes not a problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 7:31 AM

They shoud change IDE SW setting maybe. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 7:36 AM

The behaviour of the "hardware NSS output signal" is described in the Reference Manual:

Indeed, that doesn't sound like a very useful behaviour - but it is the defined behaviour.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 8:00 AM

Unfortunally it doesn t work as described in the Reference Manual. I have to add manual CS meaning that I have to add layer of software (simple modification) over the HAL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-09-18 8:21 AM