- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Can the STM32G4x1 line access external flash memor...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can the STM32G4x1 line access external flash memory? Or just the G4x4 line??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-12 11:21 AM

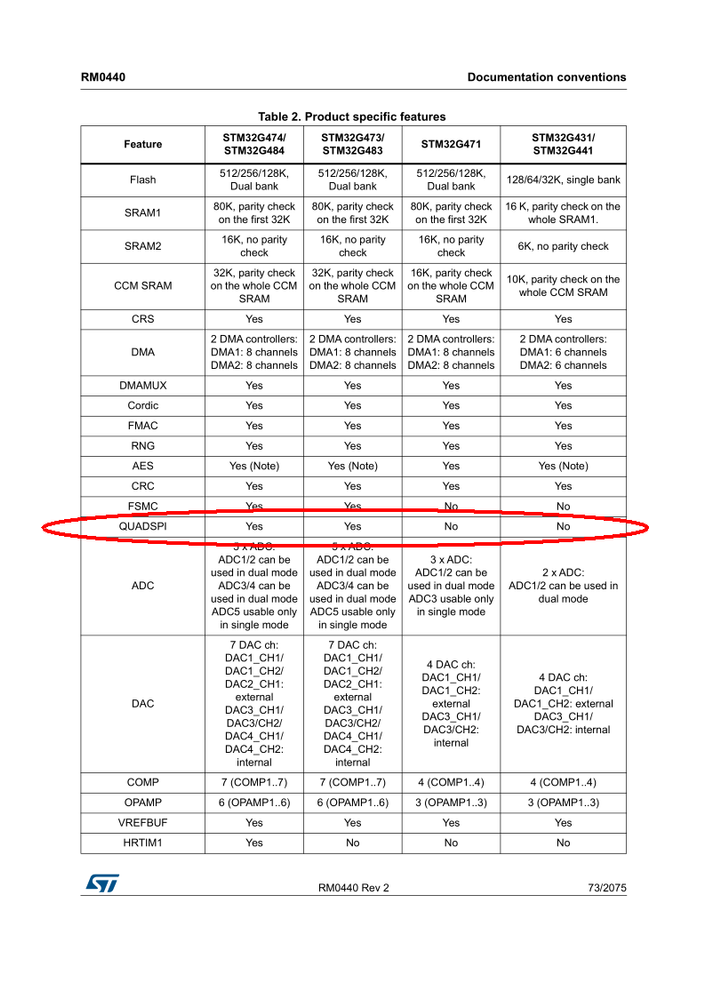

My question here is this: Can the STM32G4x1 line access external flash memory (e.g., via QuadSPI)?

My confusion is as follows: the following page:

https://www.st.com/en/microcontrollers-microprocessors/stm32g4-series.html

introduces the STM32G4x1, G4x3, and G4x4 lines. In the table (at the center of the page), Quad-SPI (for accessing external flash memory) is listed in the left column as a common feature across all three of these lines.

In addition, the slides at

indicate that "The Quad-SPI memory interface integrated inside STM32G4 microcontrollers provides a communication interface, allowing the microcontroller to communicate with external SPI and Quad-SPI memories".

In addition, Ch 19 of the exhaustive RM0440 STM32G4 Reference Manual, which describes QuadSPI, doesn't make specific mention that QuadSPI is disabled on the G4x1 line.

HOWEVER,, in (e.g.) the STM32G474VE features diagram, I see a block labelled External Interface, that mentions both FSMC and QuadSPI, where I don't seem mention of either in the features diagrams for ICs in the G4x1 family. I'm also having a very hard time finding the right pins for QuadSPI (BK1_IO*, BK2_IO*) on the G4x1 IC we are looking at using STM32CubeMX.

So... confusion.

Solved! Go to Solution.

- Labels:

-

Documentation

-

STM32G4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 3:46 PM

Standard - yes, see below. Dual, quad - not in a practical way (technically you can operate it in those modes, but it would cost extra pins and so much extra and unusual software effort that it would pay off only in some particular niche applications).

Standard SPI sFLASH access means, that you handle the whole communication protocol with the memory in software (with potential help of DMA for the bulk transfer). In contrast, the QSPI peripheral handles all protocol for read in hardware and programmer is presented conveniently with data in the native address space of the processor, as if it would be an internal (albeit somewhat slower) memory.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-12 11:53 AM

1) The datasheets of G431 and G441 don't mention QSPI in the "Communication interfaces characteristics".

2) The AF table ibid. doesn't contain a column head mentioning QSPI, nor is there any entry regarding QSPI.

This means: no. No wonder you can't find the pins for QSPI in CubeMX.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-12 2:16 PM

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-12 2:20 PM

> https://www.st.com/en/microcontrollers-microprocessors/stm32g4-series.html

> introduces the STM32G4x1, G4x3, and G4x4 lines. In the table (at the center of the page), Quad-SPI (for accessing external flash memory)

> is listed in the left column as a common feature across all three of these lines.

Indeed, this is confusing.

@Imen DAHMEN , can this picture/table please be modified accordingly? IMO the FSMC column could represent both FSMC and QSPI.

Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-12 2:33 PM

JW et al - Thank you yet again for addressing my confusions. :) - TB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 3:43 AM

Hello,

This is raised internally for correction.

Thank you for your contribution.

Best Regards

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 3:54 AM

Thanks Imen.

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 12:35 PM

Sorry guys, me again, returning to my question "Can the STM32G4x1 line access external flash memory?"

Researching SPI memory a bit futher, I easily find a ton of SPI Flash memory ICs on the market (at $2 or less, in a 5mm x 5mm or so footprint, with 4MB or more of memory, really quite useful...). I want to use one, and am still planning on using a STM32G4x1. I see that many flash memories operate over "standard SPI". For example, from https://www.digikey.com/en/articles/techzone/2019/may/why-and-how-to-expand-microcontroller-program-memory-with-spi-xip-flash

I see the following:

- Standard SPI operation: The Flash memory is accessed like a standard SPI memory device with SPI clock (SCLK), active-low chip select (CS\), serial input (SI) data and serial output (SO) data. Standard SPI bus modes 0 and 3 are supported.

- Dual SPI operation: This provides twice the data rate of standard SPI operation by using SI and SO as bidirectional data pins, designated IO0 and IO1.

- Quad SPI operation: This provides four times the data rate of standard SPI operation. Besides IO0 and IO1, WP\ and HOLD\ are used as bidirectional data pins, IO2 and IO3. In quad SPI operation, WP\ and HOLD\ features are not available.

The reference manual for the G4 has extensive discussion of a powerful Quad-SPI interface that is apparently (at least, currently) only available on G4x4 ICs (so, is not available to me with my current design).

To restate my original question a bit differently, can I use Standard SPI operation and/or Dual SPI operation to access external flash memory using a STM32G4x1, which does not have ST's special Quad-SPI interface?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 3:46 PM

Standard - yes, see below. Dual, quad - not in a practical way (technically you can operate it in those modes, but it would cost extra pins and so much extra and unusual software effort that it would pay off only in some particular niche applications).

Standard SPI sFLASH access means, that you handle the whole communication protocol with the memory in software (with potential help of DMA for the bulk transfer). In contrast, the QSPI peripheral handles all protocol for read in hardware and programmer is presented conveniently with data in the native address space of the processor, as if it would be an internal (albeit somewhat slower) memory.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 11:19 PM

thank you JW. That's clear.

- Debug STLink GDB Server v.1.3.0 - PARSE ERROR: Argument: -cp in STM32CubeIDE for Visual Studio Code (MCUs)

- STM32H563ZIT6 external loader not working in debugger in STM32CubeIDE (MCUs)

- STM32N6 Nucleo Target Not Responding After Intial Success in STM32 MCUs Products

- Ardunio GIGA R1 - STM32H747I - cubeMX configuration- fail to power on in STM32 MCUs Boards and hardware tools

- STM32N6570-DK – FSBL & Application Binary Handling and Jump to Application in STM32 MCUs Products