- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Auto Delay ADC STM32F3

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Auto Delay ADC STM32F3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-29 7:12 AM

Hello Community,

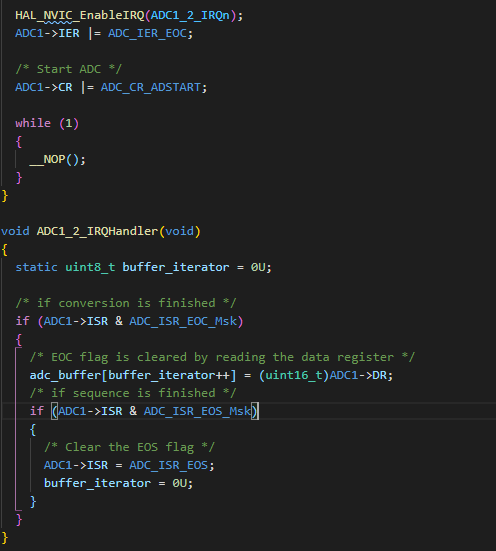

I'm currently programming a framework for the STM32F3 ADC. However I ran into a problem. I want my ADC to run continuously. Moreover I expect "long" delays between reading the channels. I thought, this is no problem, since the ADC has the Auto Delay functionality. I attached a similar program flow and like my real program, the EOS flag is always set after the delay and only buffer[0] is written. I already searched the reference manual as crazy. Can someone see my fault?

Regards

- Labels:

-

ADC

-

STM32F3 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-29 11:11 AM

Does it work if you take out the HAL_Delay(1); line? Probably all the conversions are overwriting each other. You need to use DMA for multiple channels, or be more responsive to the EOC flag.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 12:25 AM

Hmm, no it doesn't actually. It worked as I used (EOC-) interrupts for it, however I want this to be independent from DMAs and Interrupts

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 12:49 AM

This code works. But I really don't get it. I thought the Auto Delay waits with the next conversion until the DR is read (EOC flag cleared)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 1:33 AM

Don't you observe it in debugger?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 2:32 AM

I do, and the desired cfgr bits are set, however the ADC isn't stopped by the debugger. So when i break the execution and refresh the DR register, it always holds another value

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 6:17 AM

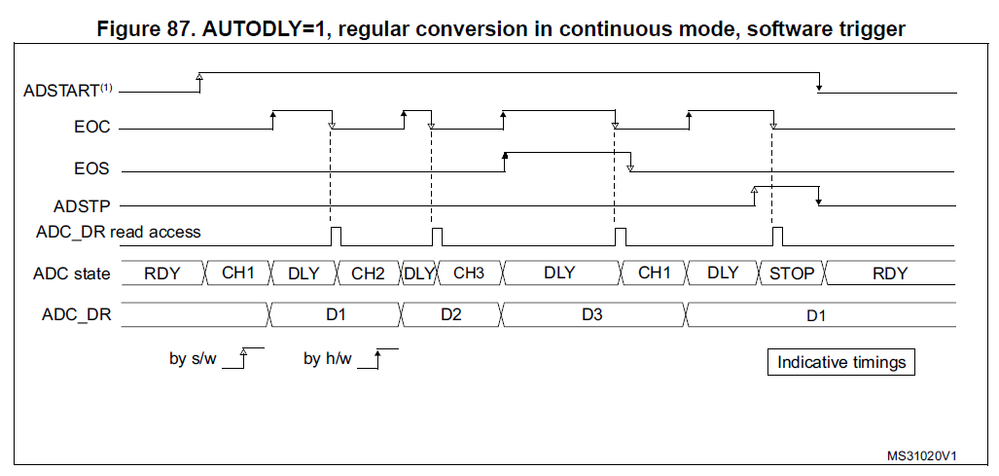

This figure suggests your original logic would work just fine:

Probably something else you're missing.

I wish the F4 had the same functionality.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 11:23 AM

>> Don't you observe it in debugger?

> I do

Okay so that's why the conversion doesn't stay in the DLY state - you read out ADC_DR by the debugger, thus clearing EOC. Exactly as in the "classical" case of UART and SPI I am talking in that link, and discussed here so many times.

Stop observing ADC by debugger, observe only the memory where the program writes the data.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-30 2:00 PM

That was also my guessing. Since it‘s a framework or a driver, it shall be debuggable. I‘m currently try to make a workaround with the discontinuous mode with n=1 and start the adc everytime after I read the reg. However, at a certain time, it doesn’t work anymore. But this is a subject for another thread ;)

thank you both anyway :)

- STM32G431 Bootloader issue in STM32 MCUs Products

- STM32F469 + AS4C4M16SA SDRAM – Read Returns Last Value with MSB Duplication Issue in Others: STM32 MCUs related

- Error: failed to erase memory on STM32F407 in Others: STM32 MCUs related

- STM32CubeIDE terminal can't connect after very first debug-session in STM32CubeIDE (MCUs)

- PWM no ouput on PB6 using ide PlatformIO in Others: STM32 MCUs related