- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- SAI - no signal on MCLK pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SAI - no signal on MCLK pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-28 09:00 AM

Hi :)

I am using SAI in TDM-8 mode, my MCU is a STM32F446RE. I want to use a PCM1681 but so far I am simply analysing the outputs. Everything seems to work fine apart from the MCLK output pin which gives me nada.

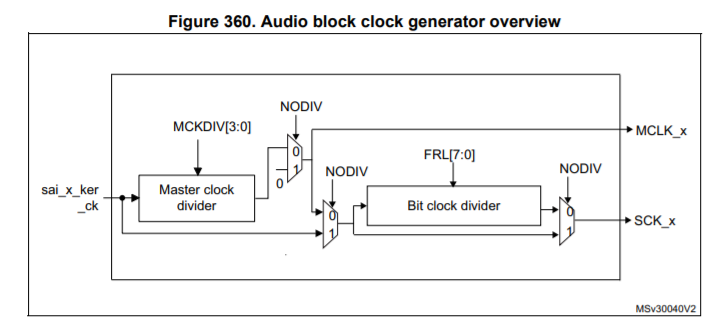

I followed what is explained in the RM0390 (https://www.st.com/resource/en/reference_manual/dm00135183-stm32f446xx-advanced-armbased-32bit-mcus-stmicroelectronics.pdf) section 28.3.8 "SAI clock generator" (pages 941 & 942).

In particular:

with:

- sai_x_ker_ck = SAI clock set in Clock Configuration in CubeMX

- MCLK_x = sai_x_ker_ck / (clockDivider * 2) or = sai_x_ker_ck if clockDivider=0

- SCK = MCLK * frame_length / 256

In my case I need 8 slots of 32 bits each per audio sample, so my frames are 256 bits long, so I have SCK=MCLK=256fs. And because I want the best accuracy possible for fs=44.1kHz, the best I could get was 0.22% with a sai_x_ker_ck of 11.289474MHz which is almost 256fs.

So in my case I have sai_x_ker_ck = MCLK = SCK, and I found that in this case the MCLK pin is not outputting. Is then the idea is simply to connect both the SCK and MCLK pins of my DAC (PCM1681) to the SCK pin of the MCU?

Thank you!

Simon

PS: in case you are wondering I am pretty sure that sai_x_ker_ck=MCLK=SCK is the reason why the MCLK is not outputting, I can get it to output fine if I reduce the frame to 128bit (then I have sai_x_ker_ck = MCLK = SCK * 2), or if I double sai_x_ker_ck (then I have MCLK = SCK = sai_x_ker_ck / 2), in this case MCLK=SCK but strangely they are opposite phase)

Solved! Go to Solution.

- Labels:

-

Audio

-

SAI

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-29 12:55 PM

Simon,

> It is strange but I am thinking it might be an actual feature that ST forgot to mention in the datasheet/DM?

Maybe.

https://community.st.com/s/question/0D50X00009XkaBlSAJ/f446-documentation-sai-clock-generator

> The only question I have really is: if SCK and MCLK are meant to be at the same speed, will a DAC work simply connecting both the MCLK and the SCK clock pins to the SCK pin of the MCU?

That of course depends on the DAC, but I'd be very surprised if it wouldn't work in this particular case.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-28 03:58 PM

So, do you see other SAI signals working? What's the primary SAI clock and how did you verify it is working?

Read out and check/post the SAI and relevant RCC and GPIO registers content.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-29 12:34 PM

Thank you for the reply Jan.

Yes I realized I did not put any info about my configuration - the primary SAI clock is the internal SAI PLL, and it works since everything else is working fine, including the SCK pin which outputs at the same speed at the master clock (and is meant to).

Like I said I am pretty sure of what I found, i.e. when sai_x_ker_ck=MCLK=SCK then the MCLK pin is not giving any signal.

It is strange but I am thinking it might be an actual feature that ST forgot to mention in the datasheet/DM?

The only question I have really is: if SCK and MCLK are meant to be at the same speed, will a DAC work simply connecting both the MCLK and the SCK clock pins to the SCK pin of the MCU?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-29 12:55 PM

Simon,

> It is strange but I am thinking it might be an actual feature that ST forgot to mention in the datasheet/DM?

Maybe.

https://community.st.com/s/question/0D50X00009XkaBlSAJ/f446-documentation-sai-clock-generator

> The only question I have really is: if SCK and MCLK are meant to be at the same speed, will a DAC work simply connecting both the MCLK and the SCK clock pins to the SCK pin of the MCU?

That of course depends on the DAC, but I'd be very surprised if it wouldn't work in this particular case.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-30 11:37 PM

Ha this is great Jan!!

You wrote:

>> MCLK stops to be output when MCKDIV=0 and FRL=255; the RM shall say this either in this subchapter, or at FRL bits description; or maybe both, as it's quite surprising.

MCKDIV=0 and FRL=255 gives sai_x_ker_ck=MCLK=SCK so that matches perfectly! At least we agree :)

You seem to have been digging deep in the SAI stuff ;)

And yes for the SCK/MCLK pins that was also what I was expecting - thanks for answer.

Anyways situation is all sorted now :)

Cheers

Simon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-27 07:13 PM

Hey Simon,

What solution did you end up with for this?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-28 02:33 AM

I'd guess, this;

> if SCK and MCLK are meant to be at the same speed, will a DAC work simply connecting both the MCLK and the SCK clock pins to the SCK pin of the MCU?

Please start a thread stating your problem with details - mcu, relevant setup, what is the expected and what is observed behaviour - and perhaps linking to this one.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-28 08:46 PM

This is actually the exact issue I'm having. Same DAC and everything except this is on an STM32F7. I will rework my PCB to connect MCLK to SCK.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-29 01:54 AM

For a prototype, can't you simply patch (cut/wire-connect) the circuit?

Can't you use a different combination of SCK/MCLK?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-29 03:59 AM

Hi ERund - is your issue that the MCLK pin is not outputting?

If so, the yes your got the reason: "MCLK stops to be output when MCKDIV=0 and FRL=255;"

And yes my solution to this was simply using the SCK pin since it outputs the same.

Simon

- STM32F446RE DAC External Protection in STM32 MCUs Products

- STM32U575ZIQ SPI behavior when enabling while slave select signal and clock are active? in STM32 MCUs Products

- While(1) Not Executing in STM32 MCUs Products

- STM32U5 OPAMP usage with sine wave with voltage offset in STM32 MCUs Boards and hardware tools

- STM32U575Q CDC USB Device Not Recognized as Virtual COM Port (VCP) in STM32 MCUs Embedded software