- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: Dual port ethernet

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Dual port ethernet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-24 01:09 AM

Hey,

I use STM32H745, I created ETH communication on the M4 core and it works well.

Now I want ETH communication with two ports, one port per core.

It is possible?

In each core before the main while, I do:

MX_LWIP_Init();

/* create new tcp pcb */

tcpb = tcp_new();

err_t err;

if (tpcb != NULL)

{

//err_t err;

/* bind echo_pcb to IP and PORT (ECHO protocol) */

err = tcp_bind(tpcb, &ipaddr, SysIP.PORT);

if (err == ERR_OK)

{

/* start tcp listening for echo_pcb */

tcpb = tcp_listen(tcpb);

/* initialize LwIP tcp_accept callback function */

tcp_accept(tpcb, PC_tcp_accept);

}

else

{

/* deallocate the pcb */

memp_free(0, tpcb);

}

}

And inside the main while, I execute MX_LWIP_Process();

For M4 core: SysIP.PORT == 4949.

For M7 core: SysIP.PORT == 4950.

IP ADDRESS, NETMASK ADDRESS and GATEWAY ADDRESS are the same for both cores.

I have no ping at all when I try to create this way.

What am I doing wrong? What should I do differently? Need to change something in CubeMX?

Thanks for the helpers!

- Labels:

-

Ethernet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-24 02:39 AM

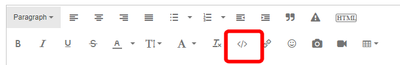

Use this button to properly post source code:

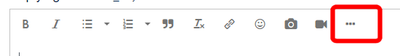

To get that extra row of icons, press this button:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-24 04:33 AM

void PC_tcp_init(void)

{

/* create new tcp pcb */

tpcb = tcp_new();

err_t err;

if (tpcb != NULL)

{

//err_t err;

/* bind echo_pcb to IP and PORT (ECHO protocol) */

err = tcp_bind(tpcb, &ipaddr, SysIP.PORT);

if (err == ERR_OK)

{

/* start tcp listening for echo_pcb */

tpcb = tcp_listen(tpcb);

/* initialize LwIP tcp_accept callback function */

tcp_accept(tpcb, PC_tcp_accept);

}

else

{

/* deallocate the pcb */

memp_free(0, tpcb);

}

}

}

MX_LWIP_Init();

PC_tcp_init();

while(1)

{

MX_LWIP_Process();

}- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-24 10:54 AM

I have limited experience with STM32 dual-core CPUs, but I believe that you cannot map a single peripheral (i.e. ETH) to both cores. It needs to be mapped/assigned to one core, and that core needs to handle the low-level ethernet stuff (i.e. ETH hardware config and IRQ handler). Then that core decides whether to send incoming packets to its own LwIP stack or somehow pass it to the other core. Likewise, there needs to be code to allow the 2nd core to "send" outgoing packets to the 1st core to actually send them. AFAIK that will be custom code in the LwIP low-level input and output functions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-25 12:07 AM

In general, is it possible to configure two ports in an STM32 MCU?

Have you seen an implementation of this before?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-28 09:24 PM

Two (or more) IP ports, yes. You can open many IP ports at the same time (as long as you have LwIP configured to have enough buffers). You just need a bind() call for each port and provide code to service each one. I do this all the time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-29 02:25 AM

There are Ethernet controllers which connect via SPI (and other interfaces) - you could use them to add extra physical interfaces?

And there are things like Wiznet & Lantronix which offload the whole IP stack; eg,

https://www.carminenoviello.com/2015/08/28/adding-ethernet-connectivity-stm32-nucleo/

https://www.lantronix.com/products-class/wired-modules/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-29 03:30 AM

@ACohe.3 wrote:Now I want ETH communication with two ports, one port per core.

Why?

Wouldn't it make more sense to have just one Ethernet port, and have the 2 cores communicate over internal inter-core interfaces?

- STM32CubeProgrammer v2.18.0 - missing DBANK/DUALBANK option bytes when cli is called in STM32CubeProgrammer (MCUs)

- STM32H733 data cache initialization issue in STM32 MCUs Products

- STM32F439ZI TCP COMMUNICATION in STM32CubeIDE (MCUs)

- build issue : undefined reference to `altcp_tls_wrap' in STM32 MCUs Embedded software

- STM32H5 Interface With Gigabit Ethernet PHY device in STM32 MCUs Products