How to change the (STLINK_V3E) MCO HSE Frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-17 11:54 PM

That is the ST-link V3 on NUCLEO-H755ZI board.

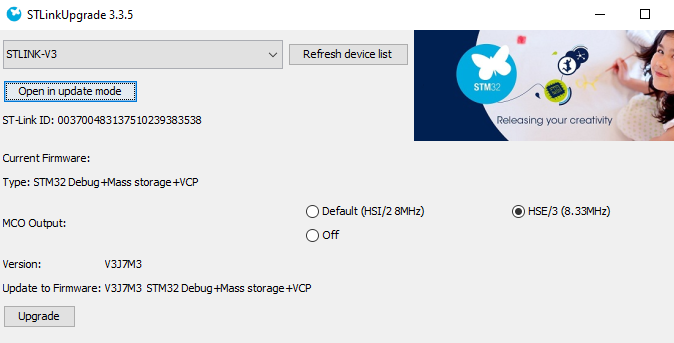

The HSE MCO option is set to HSE/3, how to change it to HSE/5.

Usually this is configurable in code, but this is ST-link firmware. If there is a way to change the division value, please some one let me know.

Solved! Go to Solution.

- Labels:

-

ST-Link

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-18 02:34 AM

Hello,

Sorry for having missed this topic. The ability to change the MCO source on STLINK-V3E boards has been added in response to another topic: ST-LINK provides 8.08 MHz instead of 8.000 on new ... - Page 3 - STMicroelectronics Community. It has been documented in RN0093 rev23 (11 may 20) and remains in the history of more recent versions. The impact on all other boards UM has been missed, concerning the UM2408 it's all the more a pity as it has been updated afterwards for other things (23 march 21) ...

Technically at that time the aim of the change was to increase the accuracy of the clock, and it has been decided (mainly for graphical interface simplification reason), to provide only a single value based on the HSE, close to the initial 8MHz, and hoping that an additional factor of 24/25 in the PLL could address most cases. We also decided to change the oscillator of the STLINK-V3EC boards back to 24MHz to fix the issue on future boards.

For this case especially, I think we will add the HSE/5 selection in STLink-Upgrade applications. I'm wondering also about the HSE/4 which could also allow other "high" frequency multiples.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-18 12:20 PM

Hello

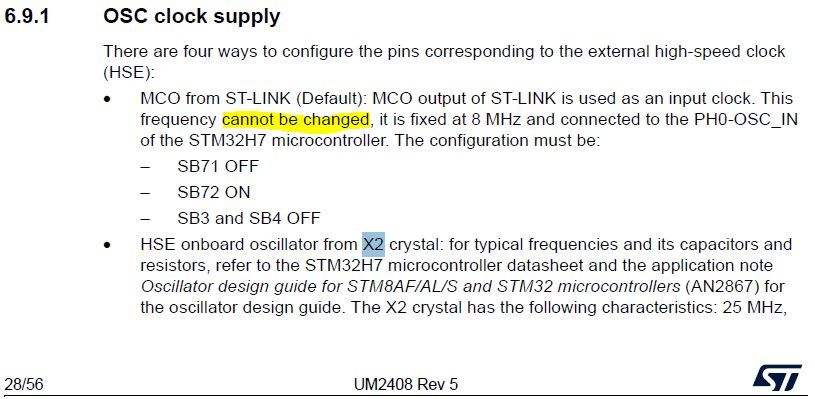

MCO clock from STLink is 8MHZ and can't be changed. Is connected to MCU's OSC_IN pin. ( HSE input)

Do you mean some other Divider PLL1 -PLL3 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-18 01:59 PM

ST-Link/V3 doesn't clock at 8 MHz

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-19 04:43 PM

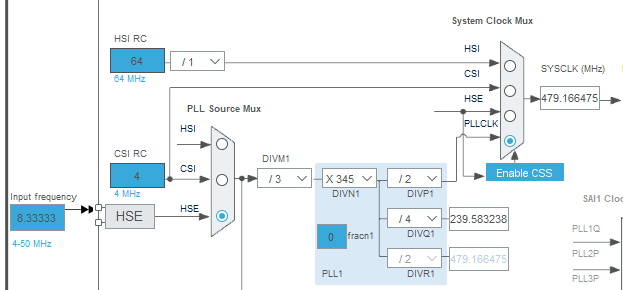

Here it is.

The PLL allows maximum multiplication of 512, which should produce (in my case) 960MHz, after that there is a /2 divider.

A PLL pre-division also exist.

DIVM1: / (1-63).

DIVN1: x (4-512).

DIVP1: / (2-128), with increments of 2.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-20 03:28 AM

Hello

I ignored this picture with STlink Upgrade MCO freq. Also user manual needs an update.

I think is not possible to take 480 from 8.333 with the existing limitations of PLL1. If DIVM1 is 5, 420 and less is ok if DIVM1 is 3 => 475 , 450, ... etc is ok.

If onboard X2 crystal is present , consider use it .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-20 04:57 PM

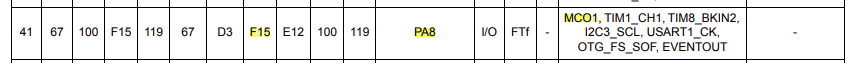

The STLINK-V3 chip is STM32F723IE, and by referring to the (MB1363-H755ZIQ-D01_Schematic) sheet 9 (also page 9) which contains (STLINK_V3E), it shows:

By further referring to the datasheet (page 76), it shows:

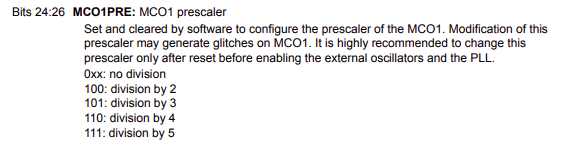

Now, by looking at page 144 in the Reference Manual we see the prescaler setting in the RCC->CFGR register:

I need to change this setting (from 3) to (2, 5, or 0 if possible for 25MHz), we should find a way to do this, maybe ST should allow this in the future firmware update, but also if someone knows a way to do this please tell me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 10:43 PM

Actually, I figured out that using the fractional part of the PLL could achieve a good result.

Using the following configuration:

DIVM1: 3

DIVN1: 345

FRACN1: 4915

DIVP1: 2

The equation is: input_frequency / DIVM1 * (DIVN1 + FRACN1 / 2^13) / DIVP1

This would lead to about: 479.99996609

With a difference about: 0.0000339 Hz (%0.0000000706)

I think this would be acceptable.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-23 01:40 AM

However there is no public way to set these parameters in the STLINK Api that I know of.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-30 08:15 AM

-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 10:13 PM

More than 4 years after ST-LINK V3 based boards came out and more than 2 years after this topic was created - of course it's too soon to ask for a correctly updated documentation from this company... Also the new forum has no ability for other users to add tags to the topic and therefore report issues. And on top of that many of the necessary tags have been removed at all (even for the topic author), including the "Bug-report" and "Documentation" in many forum sub-directories.

@Imen.D , @Peter BENSCH , excellent job, ST!