- STMicroelectronics Community

- Product forums

- Power management

- Re: STSPIN32F0A ADC misbehaving?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STSPIN32F0A ADC misbehaving?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 5:22 AM

I have run into problems with ADC of STSPIN32F0A (STM32F031C6) apparantly misbehaving.

The ADC is running on it's own 14 MHz asynchronous clock while MCU runs at 48 MHz.

After trying to measure current on the STEVAL-SPIN3202 board in 6-step setup I come to the conclusion there is too much noise to deliver smooth control.

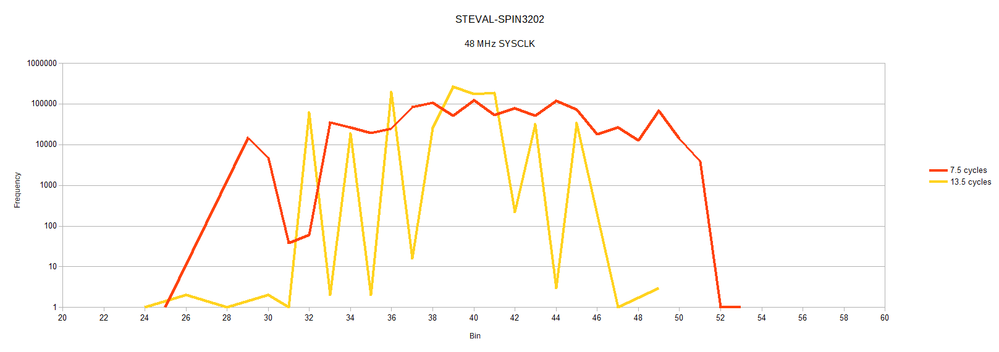

I set up a test of just reading the potmeter coupled in on ADC channel 4 on the board using different sample&hold times. What I discover is discrete errors.

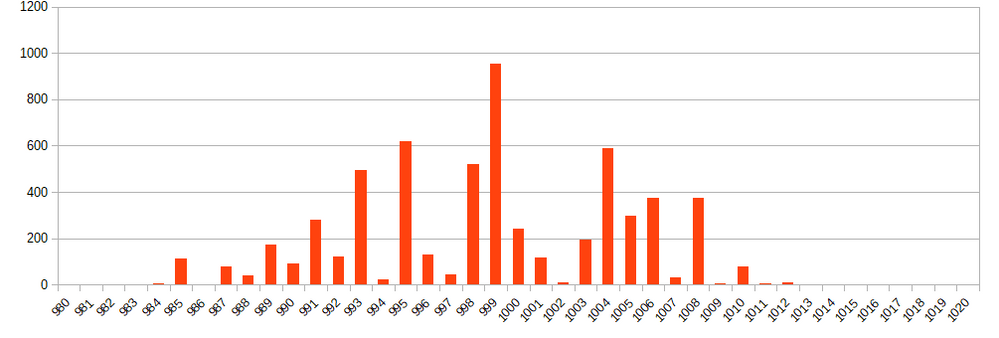

With 1000 readings at 10ms intervall of potmeter adjusted to approximately give 1000 in raw value from ADC I received data containing only the values 975, 979, 983, 987, 991, 995, 999 using 13.5 cycles capture&hold.

Looking at these in binary I see:

975 = 00000011 11001111

979 = 00000011 11010011

983 = 00000011 11010111

987 = 00000011 11011011

991 = 00000011 11011111

995 = 00000011 11100011

999 = 00000011 11100111

Lower 2 bits seem stuck at 1 and the total noise is far too high.

Measuring externally I see approximately 832mV on the input.

Keep in mind there is a 4.7nF capacitor to help buffer the signal being drawn in by the 8pF internal ADC capacitance. This should be ok for a somewhat close reading.

I cannot find any errata for the STSPIN32F0A so I am unsure if this is known or discussed.

- Labels:

-

Motor Control Hardware

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 6:58 AM

Using maximum sampling time results in some data in the blank areas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-24 2:12 PM

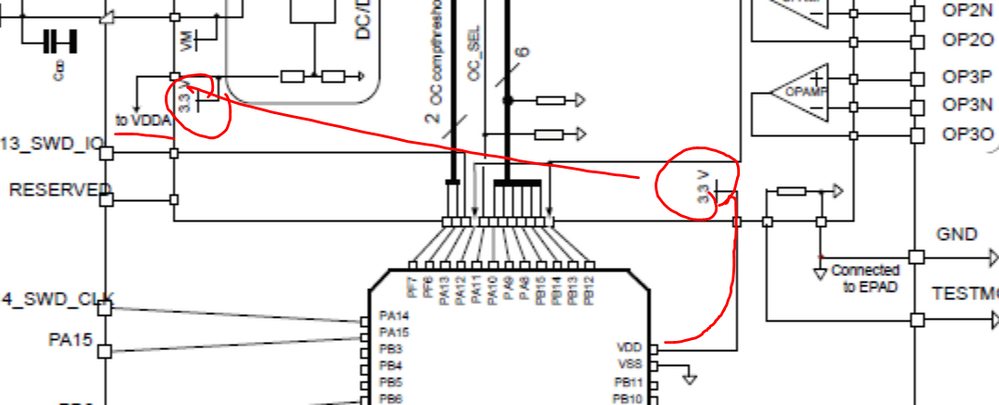

I think I narrowed it down to an internal connection in STSPIN32F0A that, due to internal connections again in the 3x halfbridge control causes VDD to be tied in with VDDA. This seems to create a lot of noise for the ADC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-24 10:47 PM

Hi, interesting finding. Based on my experience with STEVAL-SPIN3202 and SPIN3204 boards (possibly many more boards in the family) the layout is EXTREMELY POOR (all aspects of layout). You can check example here: https://community.st.com/s/question/0D53W00000U7UblSAF/critical-hw-bug-fix-steval-spin3204-board-maximum-motor-current-not-reaching-16a-as-claimed

It could be as well wrong placement or ground referencing of bypass capacitors for SPIN32F0A, current return paths not appropriate, crosstalk etc. If you can, try to check layout.

Good luck!

Stanislav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-25 1:16 PM

Seems like the entire problem is the bond for the boosters ref to VDDA. Since it shares 3.3v internally in the driver chip it should not be on VDDA. I guess bonding issues forced this?

Doing a test the chip runs even with just VDDA so VDD is getting power when using external ldo...

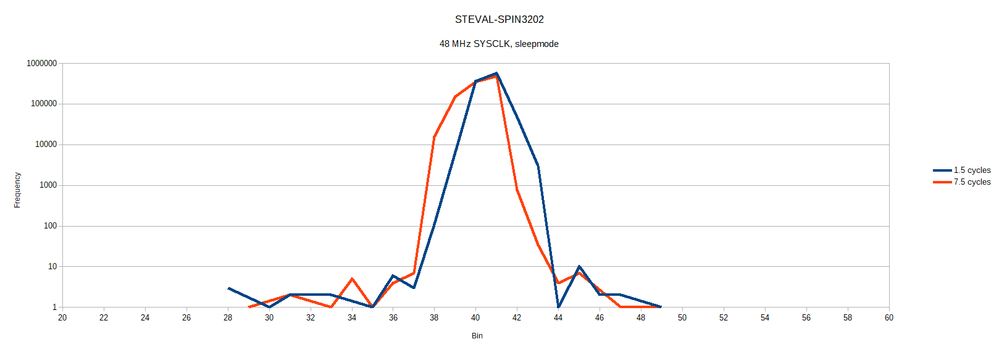

So, I put together a test using sleepmode to see if the MCU noise is what is leaking over to VDDA. It absolutely is.

Sampling is again AD3 from Speed pot, and to make it statistically significant it runs 1000000 conversions and counts all the resulting values in 1 bit wide bins before sending final result table over USART1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-24 2:15 PM

So, I've been running code on my own boards for a while now and they use a high quality 2.2 MHz switchmode regulator and filtering for the ADC. This does not help much. The quality of the sampling is still influenced heavily by the CPU clock which it would have been isolated from if the VDD / VDDA were properly separated.

- STSPIN32F0A OC protection in STM32 MCUs Motor control

- How run motor using PWM in STSPIN32F0A in STM32 MCUs Motor control

- SPI with DMA is not working in stm32g0 in STM32 MCUs Products

- VL53L4CD I2C + CircuitPython Misbehaving in Imaging (sensors)

- STSPIN32F0a: overcurrent detection (OC COMP) in FOC algorithm in Others: hardware and software