- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Using ITM printf on STM32H723 Nucleo board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Using ITM printf on STM32H723 Nucleo board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-08 08:33 AM

Hi all,

I'm tying to use the ITM printf on my STM32H723 Nucleo board in my Keil project without success. I configured the HAL with CubeMX and add the initialization for the SWD_Init(). I enabled tracing in Keil but I do not get any output.

I checked:

- SWO solder bridge SB32 on my board.

- The basic clock configuration using a PWM signal.

- I also checked SystemCoreClock variable is set to 550 MHz.

- Updated STM Link Utility to newest version

I have no clue why I can't see any output. I will attach my minimal project example as zip and some screenshots of my Keil Debug config. Hope somebody can help me with this. Keil debugger status bar is red and says no "No Synchronization"

I read the following post:

https://community.st.com/s/question/0D50X00009ce0vWSAQ/nucleoh743zi-board-and-printf-swo-not-working

Same problem without Keil is described here:

https://community.st.com/s/question/0D53W00000bebkzSAA/nucleoh723zg-itm-printf-swv-problems

I already used ITM printf on an STM32H743 processor with Keil in another project without a problem!

Regards Jonny

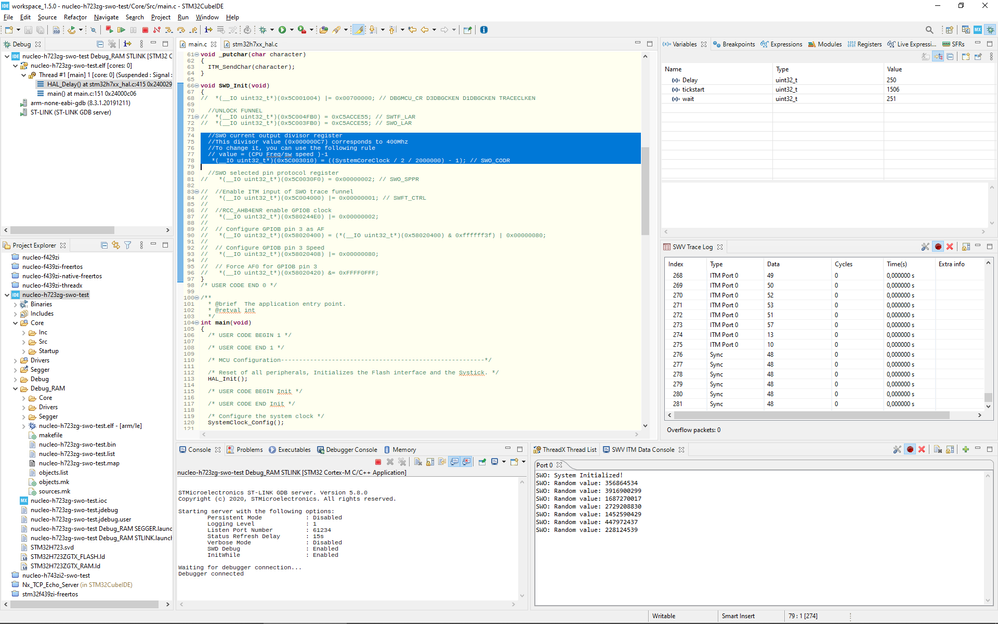

void SWD_Init(void)

{

*(__IO uint32_t*)(0x5C001004) |= 0x00700000; // DBGMCU_CR D3DBGCKEN D1DBGCKEN TRACECLKEN

//UNLOCK FUNNEL

*(__IO uint32_t*)(0x5C004FB0) = 0xC5ACCE55; // SWTF_LAR

*(__IO uint32_t*)(0x5C003FB0) = 0xC5ACCE55; // SWO_LAR

//SWO current output divisor register

//This divisor value (0x000000C7) corresponds to 400Mhz

//To change it, you can use the following rule

// value = (CPU Freq/sw speed )-1

*(__IO uint32_t*)(0x5C003010) = ((SystemCoreClock / 2000000) - 1); // SWO_CODR

//SWO selected pin protocol register

*(__IO uint32_t*)(0x5C0030F0) = 0x00000002; // SWO_SPPR

//Enable ITM input of SWO trace funnel

*(__IO uint32_t*)(0x5C004000) |= 0x00000001; // SWFT_CTRL

//RCC_AHB4ENR enable GPIOB clock

*(__IO uint32_t*)(0x580244E0) |= 0x00000002;

// Configure GPIOB pin 3 as AF

*(__IO uint32_t*)(0x58020400) = (*(__IO uint32_t*)(0x58020400) & 0xffffff3f) | 0x00000080;

// Configure GPIOB pin 3 Speed

*(__IO uint32_t*)(0x58020408) |= 0x00000080;

// Force AF0 for GPIOB pin 3

*(__IO uint32_t*)(0x58020420) &= 0xFFFF0FFF;

}- Labels:

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-08 10:16 AM

Hi!

I am struggling with the same problem!

I posted about it 1 week ago, but no ST employees responded to it.

I also performed tests with NUCLEO-H743ZI2 board and NUCLEO-H723ZG board.

The STM32H743 works as expected. With STM32H723, an evaluable SWO could not be obtained in any way.

You can read my experience at the following two links:

https://community.st.com/s/question/0D53W00000bebkzSAA/nucleoh723zg-itm-printf-swv-problems

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 07:52 AM

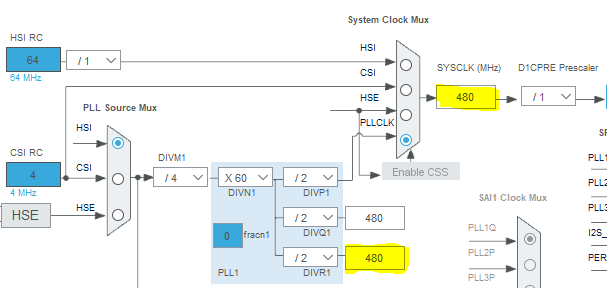

Today I used my oszilloscope to measure the frequency of the SWO signal (Resistor on SB32). I followed the guide https://www.keil.com/appnotes/files/apnt_297_v102.pdf on page 4. I discovered that the signal was running at 1MHz not at 2MHz as expected. I seams that the SWO interface runs with half core frequency. I adapted the SWD Init and now it works as expected.

Edit:

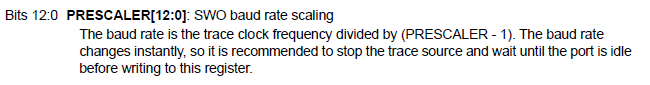

The reference manual says:

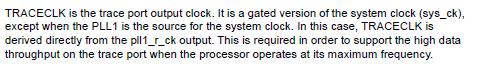

First I found this on the segger homepage:

https://www.segger.com/products/debug-probes/j-trace/technology/setting-up-trace/

"The trace clock speed (TRACECLK) is on most microcontrollers directly dependent on the CPU clock speed and is usually half of the CPU clock speed."

Then I discovered this in the STM32H723 reference manual page 3088

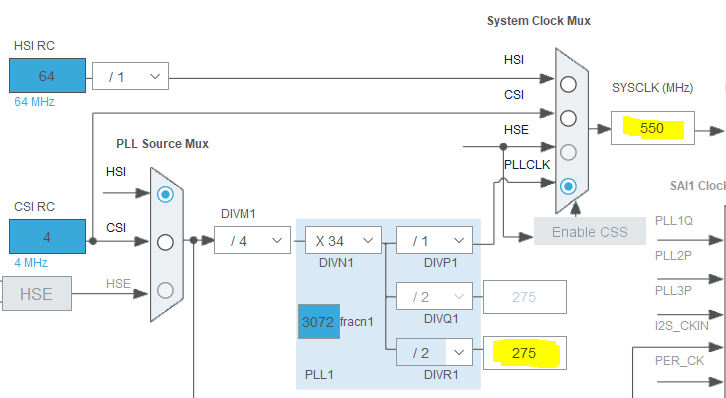

Then I compared the result with the STM32H743 clock tree of my other project:

So now I understand why my code modification is working. Maybe it is better to modify the SWD_Init code to use the DIVR1 value instead of the magic divider 2.

void SWD_Init(void)

{

*(__IO uint32_t*)(0x5C001004) |= 0x00700000; // DBGMCU_CR D3DBGCKEN D1DBGCKEN TRACECLKEN

//UNLOCK FUNNEL

*(__IO uint32_t*)(0x5C004FB0) = 0xC5ACCE55; // SWTF_LAR

*(__IO uint32_t*)(0x5C003FB0) = 0xC5ACCE55; // SWO_LAR

//SWO current output divisor register

//This divisor value (0x000000C7) corresponds to 400Mhz

//To change it, you can use the following rule

// value = (CPU Freq/sw speed )-1

*(__IO uint32_t*)(0x5C003010) = ((SystemCoreClock / 2 / 2000000) - 1); // SWO_CODR

//SWO selected pin protocol register

*(__IO uint32_t*)(0x5C0030F0) = 0x00000002; // SWO_SPPR

//Enable ITM input of SWO trace funnel

*(__IO uint32_t*)(0x5C004000) |= 0x00000001; // SWFT_CTRL

//RCC_AHB4ENR enable GPIOB clock

*(__IO uint32_t*)(0x580244E0) |= 0x00000002;

// Configure GPIOB pin 3 as AF

*(__IO uint32_t*)(0x58020400) = (*(__IO uint32_t*)(0x58020400) & 0xffffff3f) | 0x00000080;

// Configure GPIOB pin 3 Speed

*(__IO uint32_t*)(0x58020408) |= 0x00000080;

// Force AF0 for GPIOB pin 3

*(__IO uint32_t*)(0x58020420) &= 0xFFFF0FFF;

}- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 08:27 AM

The baud rate needs to match with respect to the SWO clock coming from the ST-LINK side, usually 2 MHz on the older V2 models, and perhaps 12 or 15 MHz on the newer V3 (or whatever you've ACTUALLY set it too), and the Core side clock which you're dividing down.

You probably shouldn't need the code we were using 3 years ago, because a lot of issues/bugs got fixed with respect to H7 and dual-core functionality.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 08:32 AM

I agree but that wasn't the problem here. I configured Keil for 2MHz clock and did the same in my inital SWD_Init(). But I measured 1MHz instead of 2MHz. Then I adapted the prescaler in SWD_Init() by half and everythink worked. Now I'm wondering why.

I tested configuring the GPIO pin only but that din't work for me. It only works with the SWD_Init() code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 10:57 AM

@JSchu.5: It seems that only the divider needs to be set correctly. I commented out all other register changes from SWD_Init, and SWV still works.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 11:51 PM

@PTiha so half clock frequency is working for you as well?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-10 12:25 AM

Yes, it works!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-10 03:43 AM

I also reported the problem on the SEGGER forum, I got the following answer:

"Thank you for your inquiry.

I looked into this.

For the STM32H72xx and H73xx devices, we do not set some critical registers when SWO is active,

but we do so on STM32H74, etc.

This is why it is working on your H74 but not on the STM32H723ZG.

A fix will be part of the next patched release planned for Friday, this week."

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-17 02:53 AM

Does anyone have any new information about the SWO speed / divider anomaly?

SEGGER promises a J-Link patch for the next two weeks.

Where can I find accurate information about the changes affecting STM32H723?

- Issue with Operating Two VL53L5CX Sensors on the Same I2C Bus - Nucleo F401RE in STM32CubeIDE (MCUs)

- Help understanding why my UART printf actually works - linker query in STM32 MCUs Embedded software

- STM32WL to microSD Card FR_NO_FILESYSTEM Error Help. in STM32 MCUs products

- Please guide me in STM32 MCUs products

- [STM32H563] NetXDuo TCP Echo Server only working in Debug mode (fixed IP address) in STM32 MCUs Embedded software