- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32F205xx timer 1 output compare to generate Ste...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F205xx timer 1 output compare to generate Step output for stepper motor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-28 03:45 AM

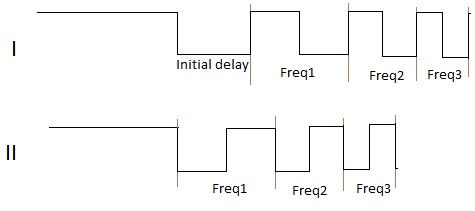

I am using timer1 channel 1 as output compare, to generate a pulse of variable period.

Desire output � In the beginning the output remain low for 4 ms(delay period) and then pulses of variable periods as 5.8, 3.6, 2.7,2.3, �. The desired time periods are stored in RAM. (Frequency range 170 Hz to 1.5 KHz)

The timer clock is configured to 1 MHz frequency. The output mode is set to toggle mode and the polarity is set to active high. The capture compare interrupt is enabled.

And the capture compare register is set to delay period and then in next interrupt, thecapture compare

register set to first period and next period will be updated after the one pulse is completed.The problem facing is that the beginning delay period is variable and sometimes missing.

If initial delay is not missing then the following output periods are correct as expected. If the low period is missing then the first period start from low rather than high which results in wrong steps

I is the correct expected output, II is wrong one.

- Labels:

-

STM32F2 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 10:13 PM

I've observed this too. Can you share a solution please?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 11:29 PM

Post minimal, but complete compilable code exhibiting the problem.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-16 12:37 AM

Thanks for the offer JW. But if you have the knowledge I'd first like some theory please.

The MCU's an STM32F0. Its software outputs a waveform using OC in toggle-mode and with DMA of a table of varying length and values to the timer's ARR. The timer is in count-up mode. The compare value is fixed at 0. Just ARR changes. ARR is not buffered. The output pin must idle high.

A new waveform must be able to start while an earlier waveform is in progress, in which case the earlier waveform stops abruptly and the new one starts.

The problem occurs when the previous number of toggles is odd.

I'm looking for method to "reset" the toggle so the first pulse of the waveform is low.

Thanks

Alister

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-16 06:01 AM

It's hard to aim at a moving target. You did not mention DMA nor interrupting previous transfers, and none of that is mentioned in the original post either. It's much easier to discuss existing complete code, you can't then come up with new surprising facts.

Your problem may be related to DMA request which the timer has previously issued but which haven't been handled by the DMA unit yet (as it is disabled or has completed all transfers). This is held in a latch which is not visible to the user, and is cleared by clearing the respective DMA enable flag in TIMx_DIER.

JW

[EDIT] https://community.st.com/s/question/0D50X00009XkaAtSAJ/how-to-clear-pending-dma-request

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-17 10:02 PM

This resets the toggle state.

// Reset the output state to idle (HIGH) and the next toggle to active (LOW)

// by changing modes (1) to force inactive and (2) back to toggle.

// Only works if the timer's enabled.

uint16_t tmpccmr1 = htim1.Instance->CCMR1 & ~TIM_CCMR1_OC1M;

htim1.Instance->CCMR1 = tmpccmr1 | TIM_CCMR1_OC1M_2;

htim1.Instance->CCMR1 = tmpccmr1 | (TIM_CCMR1_OC1M_1 | TIM_CCMR1_OC1M_0);

Regards

Alister

- DMA and OC MODE in STM32 MCUs Motor control

- Server error 61234 due to timer configuration on NUCLEO F401RE and STM32F103C8TX in STM32 MCUs Motor control

- How to generate and control a PWM with registers (NO HAL) in STM32F446RE? in STM32 MCUs products

- Generating specified number of pulses using PWM in STM32 MCUs products

- Generate velocity curve in STM32 MCUs products