- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- External LSE clock tr/tf is lower than tr/tf of ex...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

External LSE clock tr/tf is lower than tr/tf of external HSE clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-20 11:03 PM

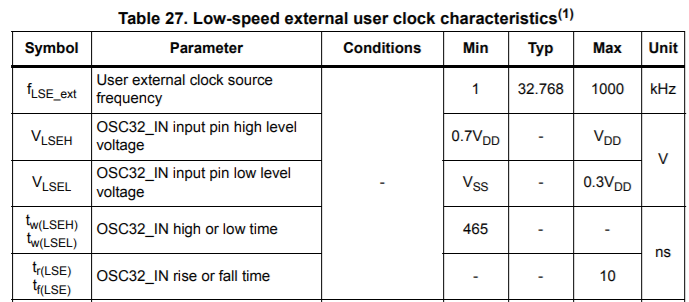

We would like to know if there's a typo for tr/tf (10 ns max) of OSC32_IN in the following STM32L151x data sheet table:

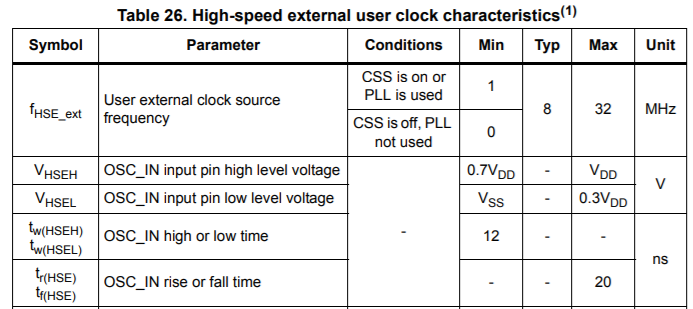

The reason we believe the above tr/tf value is a typo because the tr/tf for a high speed clock is twice as long(20 ns max) :

We are trying to feed an external 1.8V swing 32.768 kHz clock in to OSC32_IN from a micro power oscillator which can only support rise/fall times of 30 ns.

Will this work?

Thanks,

JP

#fall-time-stm32l1 #osc32_in #rise- Labels:

-

STM32L1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-24 03:18 AM

Hello

Parvereshi.Jehangir

,In external clock mode the LSE input is a simple logic gate without hysteresis.

To avoid glitch in this mode, it is better to use a fast transition signal. This

is the reason why it specified 10ns for LSE.

The situation for HSE is different since in external clock mode there is ahysteresis and the input signal can be slower.

You can

try and check the glitches in your specific application, but we will not guaranty anything on our side.

Best Regards,

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-29 09:43 AM

Hi Imen:

I would think that for a slower clock rate a slower transition should be allowed.

Looks like ST had decided to implement hysteresis on a faster clock input and not on the slower clock inputs.

Thanks for the confirmation.

TimeIT

- STM32U5G9-DK2 - Power the board using external 5V in STM32 MCUs products

- Need support in using PSRAM as internal RAM using memory mapped mode using QSPI in STM32 MCUs products

- can Ewarm project be opened in Keil or CubeIDE ? in STM32 MCUs Boards and hardware tools

- STM32L4P5VGT - CDC, MSC and Pen Drive Support on USB in STM32 MCUs Embedded software

- Touchgfx base classes on external flash memory in STM32 MCUs TouchGFX and GUI