- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32F415RGT ART Accelerator

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F415RGT ART Accelerator

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 05:32 AM

Hello,

in your first project we use a STM32F415ZGT without any problems. Then we switch to the smaller version STM32F415RGT in a new design. With the same source code we got some times a hard fault when die MCU is booting up.

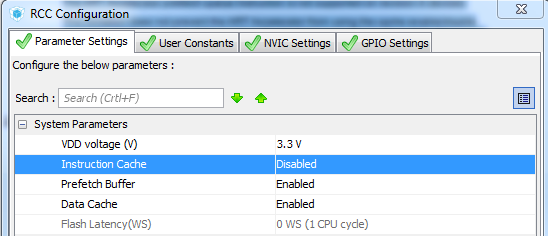

After two or three days of software and hardware bug finding and trying different versions of CubeMX and F4 firmware we find a solution to disable the Instruction Cache in CubeMX:

After that your simple LED blink code runs fine without any hard fault.

Errata sheet lists a bug in Revision ''A'' devices for the ART Accelerator:

ART Accelerator prefetch queue instruction is not supported

Description

The ART Accelerator prefetch queue instruction is not supported on revision A devices.

This limitation does not prevent the ART Accelerator from using the cache enable/disable

capability and the selection of the number of wait states according to the system frequency.

Workaround

�

Revision A devices: none

�

Revision Z and 1 devices: fixed.

We found out that your STM32F415RGT is at Revision ''2'' and that revision is not listed in fixed devices.

Is this bug still existing in Revision ''2'' devices? And when not: Do you have any solution to your problem?Best regards

#vssa #gnd #ferrite-beads #vssSolved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 09:16 AM

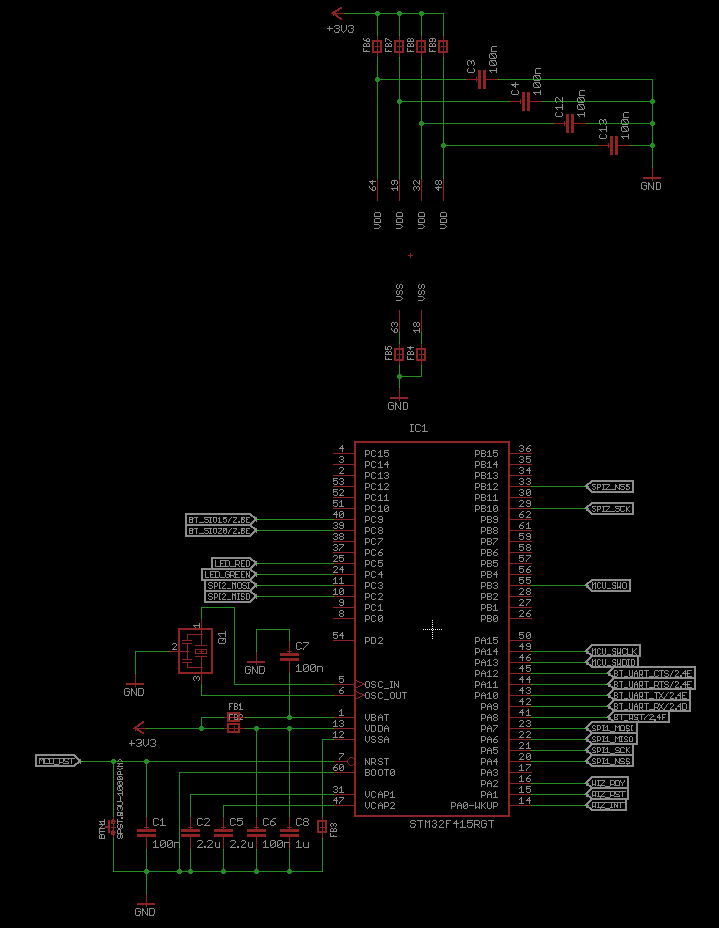

I'm not sure I'd put beads between the grounds; but I'm sure if I'd do that I'd put the capacitors *after* the beads, directly onto the mcu VSS pins. Most of them at least; and certainly those on VCAP pins.

Can you please try bypassing those beads?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 06:11 AM

What does DBGMCU->IDCODE report?

What frequency and wait states are being used?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 07:42 AM

IDCODE = 0x10076413

SYSCLCK = 168 MHzWS = 5 (6 CPU cycle)- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 08:23 AM

Is the supply voltage 3.3V and is it stable and well-decoupled? What's the voltage on the two VCAP pins, are they properly connected? Is PWR_CR.VOS=1 all the time? Are all GND/VCC pins connected properly, including the analog ones and VBAT?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 08:29 AM

Looks Ok, I disable prefetch on the 0x411 parts (0x20006411) as there is a critical path in the cache that doesn't work properly across voltage/temperature.

As Jan indicates the next place to look would be the VOS settings, and VCAP pins, making sure you have the right voltages there and adequate bulk capacitance.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 08:46 AM

We have tested three different power supplies for 3.3V and they are stable and works well with ZGT designs.

This is your shematic:

The FBx parts are ferrit beads for decoupling, type: TDK MMZ2012R601AT000.

I will check VCAP, PWR_CR:VOS and post.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 08:53 AM

The core powers from the 1.25V rail, CMOS has aggressive current draw at clock edges. You typically want low ESR, larger physical size capacitors for the VCAP pins

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 09:02 AM

Now we are using ceramic capacitors with very low ESR same as in the ZGT desings.

We will try to place larger ones. Thank you.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 09:10 AM

I would lean toward 0603 size.

Are you using GCC? The issues observed with the problem F2/F4 parts tended to be triggered more frequently with GNU/GCC based chains. Can't say I've seen any reports on issues on parts currently being distributed.

The FLASH wait states can be increased, but that is not associated with the prefetch issue where the cache attempts to deliver data within the current cycle (ie 0 cycles, vs 1 cycle SRAM)

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-08 09:16 AM

I'm not sure I'd put beads between the grounds; but I'm sure if I'd do that I'd put the capacitors *after* the beads, directly onto the mcu VSS pins. Most of them at least; and certainly those on VCAP pins.

Can you please try bypassing those beads?

- Need to confirm how FMAC loads\consumes coefficients on STM32G4 in STM32 MCUs products

- STSPIN based Motor Controller acceleration and deacceleration setting in Torque Control in STM32 MCUs Motor control

- STM32F756VGH6 problem running 2 timers at the same time in STM32 MCUs products

- STM32F756VGH6 register based interrupt syntax. in STM32 MCUs products

- Screen flickering while using TFT-LCD with LTDC in STM32 MCUs products