- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Re: I am trying to build up a QSPI connection with...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I am trying to build up a QSPI connection with the STM32H7 Nucleo Board (H743zi2). I generated the keil project(setup with CubeMX). Am measuring the CS and CLK with my oscilliscope & I cant see anything for QSPI clk more than 30MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 1:36 AM

I have attached the main file.

I am using nucleo 144 board and have setup the stm32 core for 480MHz(max), so max QSPI clock allowed is 240M/2=120MHz. But am not able to generate clock pulses if I set QSPI clock prescalar less than 8 (30MHz). I have tried for different qspi clock source selection.

Please help me to fix it. Is there anything am missing?

What is the maximum allowable qspi clock frequency in nucleo h743?

- Labels:

-

QSPI

-

STM32CubeMX

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 1:52 AM

Pretty sure I've run the interface close to 100 MHz, tends to depend on the flash IC, and the dummy cycles required at different rates. Also H7 supports DDR/DTR

Make sure to enable the IO compensation block, and back off slew rate setting on short wiring.

Your wiring/interfacing into the NUCLEO might be a limiting factor also, signal integrity becomes a big issue as clock rates go higher.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 1:58 AM

I have connected PCB of flash IC which supports upto 108MHz.

Now I am testing only with nucleo board by removing flash IC interface and measuring the wave forms in logic analyzer. Still am not able to see any clock pulses/chip select lines.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 2:49 AM

What's the model of your logic analyzer which you expect can capture 100 MHz waveform?

Afaik QSPI can be clocked somewhere around +100 MHz, independently from bus clocks. All the timings contraints are in papers.

My bit of advice: simplify: set clck to 1 MHz, and get flash ic talk at this speed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 3:16 AM

Yeah, I think I'd be using a high speed scope and 10X probe

If integer dividers on the STM32's are inflexible you can change the clocks via the PLL, and say run the H7 at 300 MHz to generate 150 and 75 MHz sources, or 266 MHz for 133 and 66 MHz.

Some of the H7 DISCO and EVAL board has QSPI examples as part of the BSP, you should review the HAL examples.

Been a few months since I was tinkering

https://community.st.com/s/feed/0D50X0000BSaahHSQR

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 4:21 AM

Nah just as I understand OP is struggling within possible issues: QSPI desired config, talking to flash ic, capturing waveform theory, signal integrity carnage. By setting clock to 1 MHz last two issues are removed. If the first two issues are resolved, then just bump up frequency and deal with latter comfortably. Q/SPI is nice that fitting timings alterations are possible in contrast to eg. USB.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-20 8:20 PM

Hi,

Thank you for the suggestions.

Here are some more inputs:

Nucleo H743 isrunning at 480MHz. Am using LogicStudio16 (500MHz) to analyze QSPI signals.

Am able to see QSPI CLK/ send data when QSPI prescalar is greater than or equal to 8.

My requirement is to communicate with flash IC at more than 100MHz (QSPI). So I need help to resolve the issue.

Screenshots were taken when flash IC PCB is not connected to nucleo stm32 H743.

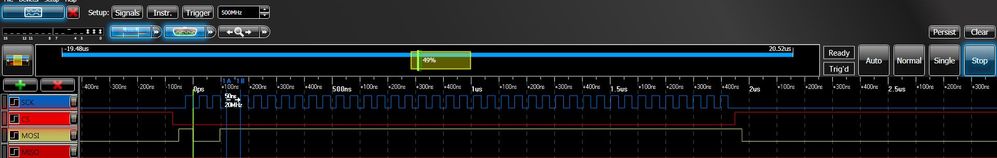

When clock prescalar is 11:

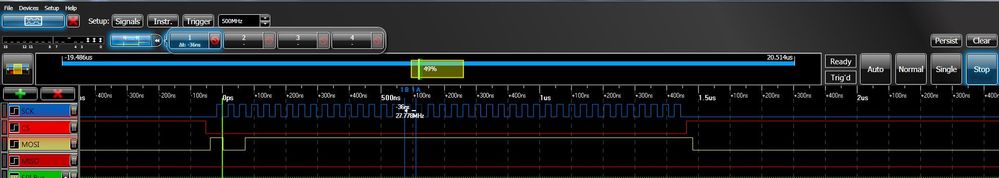

When qspi clock prescalar is 8

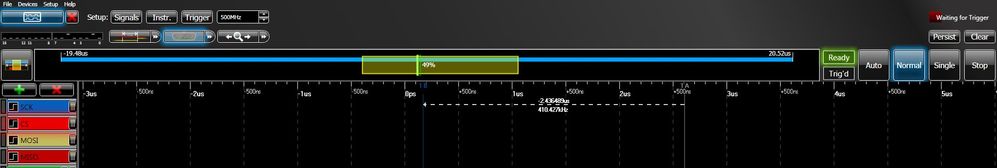

When qspi clock prescalar is 7

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 1:10 AM

QSPI pins gpio OSPEEDR register should be "very high"? Can't tell what's the value from the code. Compensation cells enabled?

So you do run "qspi kernel clock" directly from PLL? What "prescaler" are you talking about? The one from QSPI CR register?

Maybe look at your device Datasheet "6.3.18 Quad-SPI interface characteristics"

My guess is you cannot throw 480 MHz at "qspi kernel clock" but max 100/130 MHz and then have it prescaled or not.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 1:39 AM

Am running H743 clock from PLL (=480MHz). So max QSPI clock available is 240/((prescalar=1)+1)=120MHz

QSPI kernel clock source is default, 00=rcc_hclk3 in QSPI CR register. I have also tried with PLL1_Q_CLK source.

Previously i mentioned about qspi prescalars (one from QSPI CR register)

Currently I have tried with "medium" and "low" values for QSPI pins gpio OSPEEDR register. Will try with "very high" and update. - SOLVED.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-21 2:10 AM

"Am running H743 clock from PLL (=480MHz). So max QSPI clock available is 240/((prescalar=1)+1)=120MHz"

Max QSPI max clock isn't stated by what you do, but what is written characteristics in papers, which you clearly haven't read yet. When you exceed the max constraints, the system sometimes may, or may not work; afaik that's what you are experiencing.

"I don't have any idea about " Compensation cells"? Is this about specifying alternate function to qspi gpio pins???"

Open your device Reference Manual, ctrl-f "compensation", this will lead you to gpio subsection. Afaik there exists 1 HAL function, which does it for you, but can't tell more, i don't use it. That's some mysterious block somehow which affects the drive of gpios for high speed.

That's why I have adviced to lower the clock to "safer" frequency, to not bother with such issues for now.

In my thing I've straight run QSPI kernel clock from pll1 Q output with 100 MHz and prescale it in CR register. Never had any issues with clock.

- Network connection failed in Cubeide in STM32CubeIDE (MCUs)

- Network connection issue in cube ide in STM32CubeIDE (MCUs)

- STM32H745ZGT6 Unable to Connect in STM32CubeProgrammer (MCUs)

- Firmware loading error on STM32WL, incorrect memory erase in STM32CubeProgrammer (MCUs)

- "Dwarf Error" error after new installation in STM32CubeIDE (MCUs)