Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- HAL_RCC_GetPCLK2Freq() returns incorrect value whe...

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

HAL_RCC_GetPCLK2Freq() returns incorrect value when D2PPRE2 is set to divide by 2

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-12-12 4:52 PM - edited 2024-12-12 5:00 PM

Hello,

I am working on a project with the STM32H750 microcontroller using CubeMX-generated code and HAL library. My system clock configuration is as follows:

- HCLK: 240 MHz

- PCLK2: Configured via D2PPRE2

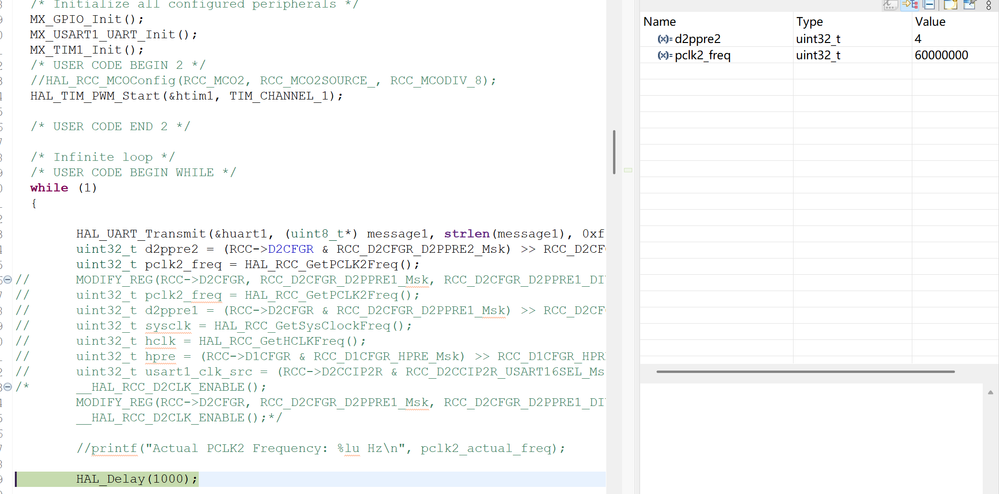

I encountered an issue related to HAL_RCC_GetPCLK2Freq() and UART configuration. Here is the detailed description:

Issue Description

- When D2PPRE2 (APB2 prescaler) is set to no division (DIV1), HAL_RCC_GetPCLK2Freq() correctly returns 240 MHz, and the UART works as expected at the configured baud rate (e.g., 115200).

- However, when D2PPRE2 is configured to divide by 2 (DIV2):

- HAL_RCC_GetPCLK2Freq() still returns 240 MHz (unaffected by the prescaler).

- The UART actual baud rate becomes half of the configured value (e.g., if I configure 115200, the actual baud rate is 57600).

- This indicates that the prescaler is applied to PCLK2 in hardware, but the HAL function does not account for it correctly.

Steps to Reproduce

- Configure D2PPRE2 to DIV2 in CubeMX.

- Initialize UART with a baud rate of 115200 using HAL_UART_Init().

- Measure the actual UART baud rate using an oscilloscope or logic analyzer.

STM32CubeIDE Version: 1.17.0

Labels:

- Labels:

-

RCC

-

STM32CubeMX

-

STM32H7 series

-

UART-USART

0 REPLIES 0