- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Re: DMA integration with Timer to control PWM is n...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DMA integration with Timer to control PWM is not sending data

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-18 07:01 PM - edited 2024-03-18 07:40 PM

Hello All,

I am using the STM32L011K4 to control the PWM duty cycle through the use of the DMA.

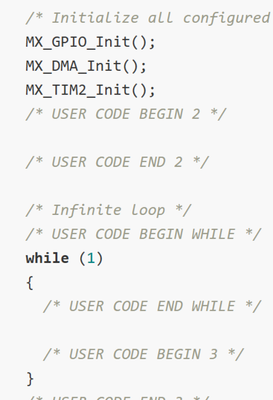

I have gone through my register initialization to ensure that the registers are being configured correctly and I have gone through and used the solution from this post: https://community.st.com/t5/stm32cubemx-mcus/ll-dma-burst-to-a-timer-not-working-on-stm32h7/m-p/137972 to initialize my DMA first, despite this the system is not working.

I have confirmed through the example code section and reading through the reference manual that the steps I am taking are indeed correct and nothing additional needs to happen. I think my mistake is something not configuring correctly despite me verifying the main settings outline the manual are verified and correct.

Further, I have verified that if a PWM is initialized the correct signal is being produced on TIM Channel 3, but I am unable to change it.

I am currently using the timer 2 burst registers to set the new duty cycles in CCR3.

I have attached my code.

UPDATE: I have found that the DMA trigger was not occuring when using I have found one issue with the DMA was that is was not being triggered from ```LL_TIM_EnableDMAReq_UPDATE```, when I enabled ```LL_TIM_EnableDMAReq_CC3``` the interrupt started working.

Correct me but isn't the UPDATE enable suppose to trigger the DMA when the timer autoreloads? Why didn't that mechanism trigger the DMA? THE CC3 enable triggers when the PWM duty cycle changes, but that isn't necessarily the best implementation nor my intention with the design.

Solved! Go to Solution.

- Labels:

-

DMA

-

STM32L0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-18 08:35 PM

> Correct me but isn't the UPDATE enable suppose to trigger the DMA when the timer autoreloads? Why didn't that mechanism trigger the DMA?

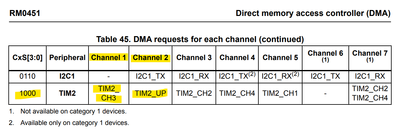

You have set up DMA channel 1 to trigger on request 8 which is TIM2_CH3. If you want DMA to be triggered by the timer update event, you need to use TIM2_UP which is on DMA channel 2 request 8.

Does that get you to where you need to be?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-18 07:20 PM

> I am currently using the timer 2 burst registers to set the new duty cycles in CCR3.

Where are you doing this exactly? I only see code which initializes TIM and DMA but doesn't actually start them. I don't see any buffers for CCR3 data, or the start of any DMA transfer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-18 07:41 PM

Apologies, I accidentally uploaded the wrong files. I have updated the correct files. Also, I have updated the post with the cause of the issue, but I do not understand where my logic is failing me.

I appreciate any help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-18 08:35 PM

> Correct me but isn't the UPDATE enable suppose to trigger the DMA when the timer autoreloads? Why didn't that mechanism trigger the DMA?

You have set up DMA channel 1 to trigger on request 8 which is TIM2_CH3. If you want DMA to be triggered by the timer update event, you need to use TIM2_UP which is on DMA channel 2 request 8.

Does that get you to where you need to be?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-19 05:36 PM - edited 2024-03-19 05:46 PM

Hey TDK that is exactly what it was. It was not obvious to me that was the case.

Thank you for clarifying this for me.

- 'undefined reference to..' error, after defining in main.h and creating a function. in STM32CubeIDE (MCUs)

- Reemission of GetID command. STM32CubeProgrammer CLI. in STM32CubeProgrammer (MCUs)

- DMA integration with Timer to control PWM is not sending data in STM32CubeMX (MCUs)

- NetXDuo and ThreadX : Increasing number of TCP Server response in STM32CubeIDE (MCUs)

- Firmware Update in STM32CubeProgrammer (MCUs)