- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Wrong flash latency from CubeMX with STM32F302...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Wrong flash latency from CubeMX with STM32F302CC?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-19 10:51 AM

My program crashes with the following error in TrueStudio:

''Program received signal SIGTRAP, Trace/breakpoint trap.

0xfffffffe in ?? ()''The fault occurs in line 692 of stm32f3xx_hal_rcc.c:

__HAL_RCC_SYSCLK_CONFIG(RCC_ClkInitStruct->SYSCLKSource);

If I change

HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_0)

to

HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_1)

everything works fine.

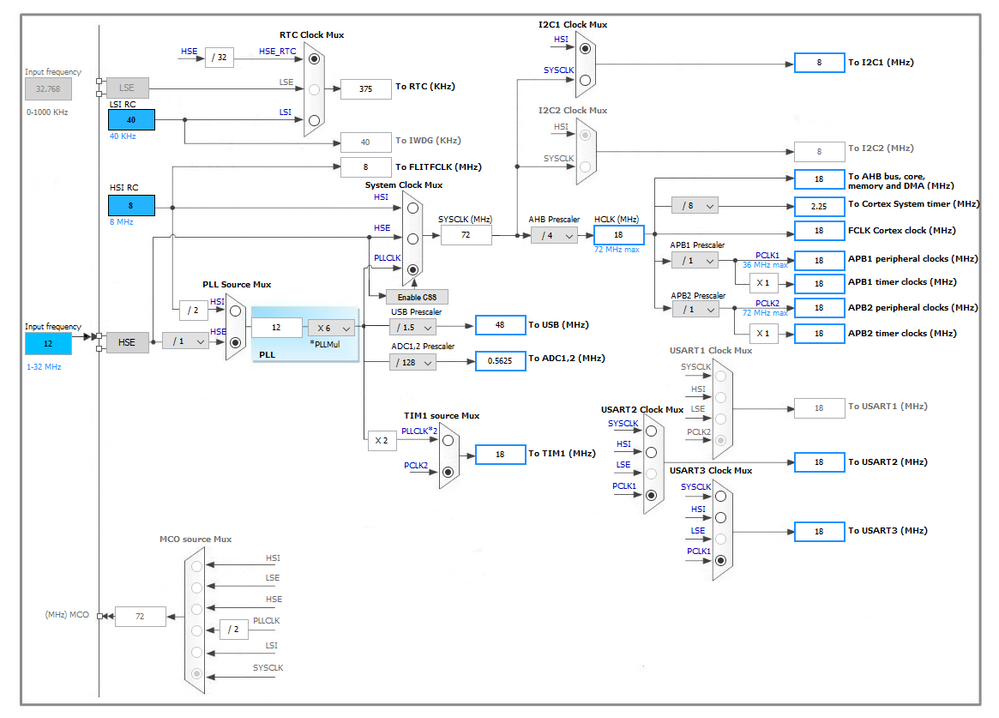

I use an external 12 MHz clock source and this configuration in CubeMX 4.25.1:

According to RM0365 the flash access time depends on HCLK not SYSCLK like in RM0008 (STM32F1...), but I tried two other configurations which indicate that flash latency should rather be set according to SYSCLK:

SYSCLK = 72 MHz, HCLK = 9 MHz -> program crashes

SYSCLK = 48 MHz, HCLK = 12 MHz -> works

Did I overlook something else or is this a bug in the reference manual / CubeMX?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-20 02:02 PM

Yes does seem a bit odd that the processor can't run at 18 MHz without zero wait states on the flash. Certainly would suggest that the flash or prefetch is running faster than advertised.

What's the power profile look like at 72 MHz with you sleeping a lot?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-20 04:43 PM

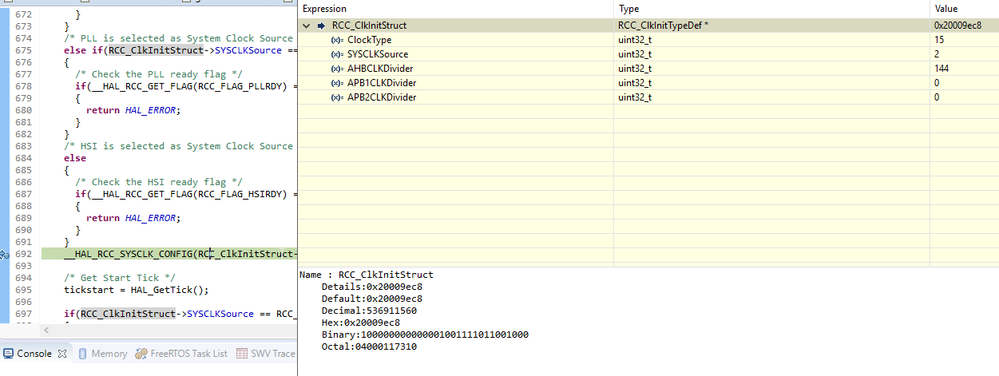

Is RCC_ClkInitStruct properly initialized (i.e. filled all its fields)?

__HAL_RCC_SYSCLK_CONFIG(RCC_ClkInitStruct->SYSCLKSource);

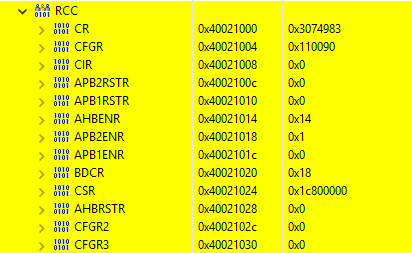

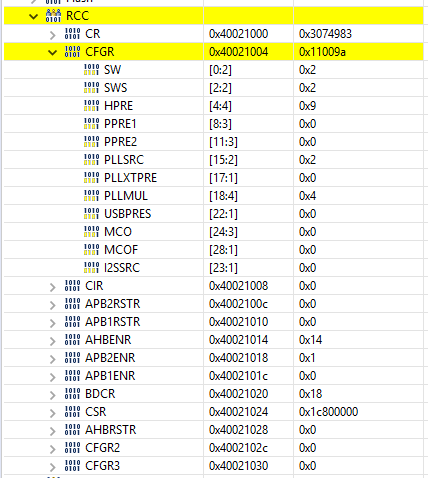

Read out and check/post the RCC registers' content just before that line.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-21 12:36 AM

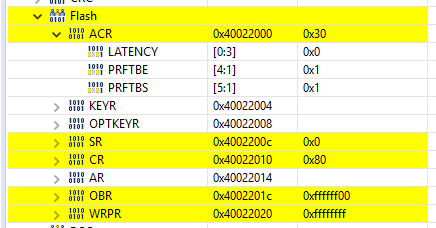

Before __HAL_RCC_SYSCLK_CONFIG:

After __HAL_RCC_SYSCLK_CONFIG:

RCC_ClkInitStruct:

For measuring the power profile at HCLK = 72 MHz I inserted ''while(1);'' before the ''MX_''-functions which configure the

peripherals.Standby current = 17 mA (probably consumption of external circuits)

Sleep current = 25 mA - 17 mA = 8 mA

Run current = 40 mA - 17 mA = 23 mA

VDD is 2.85 V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-21 05:49 AM

I can't see any obvious problem.

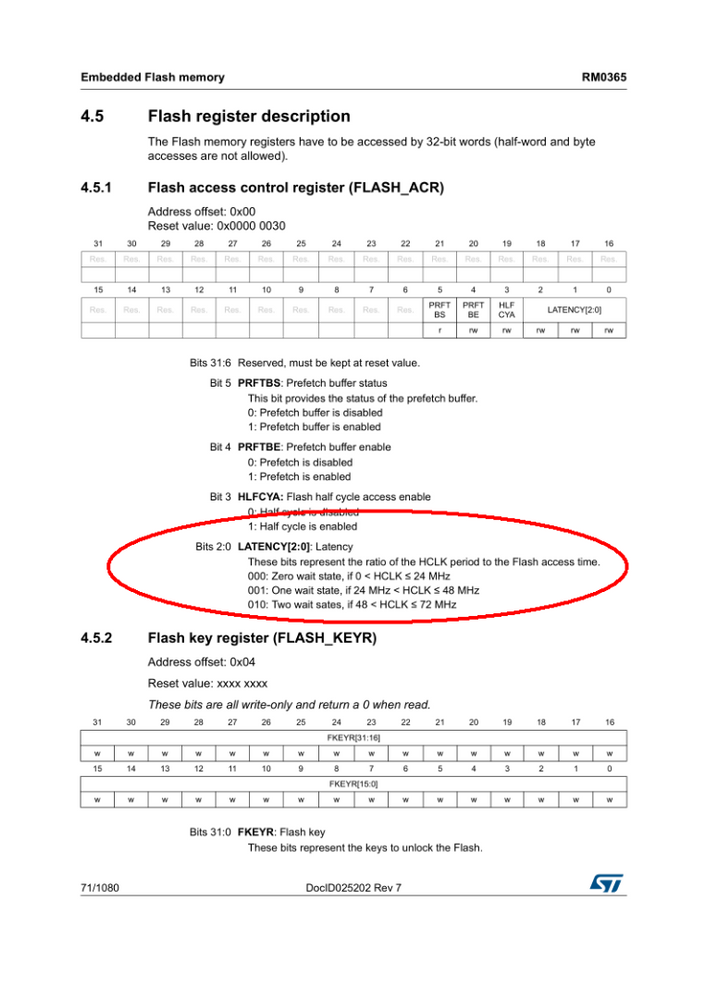

One more thing from reading the RM:

The prefetch buffer must be kept on (FLASH_ACR[4]=’1’) when using a prescaler different from 1 on the AHB clock.

Can you please read and check FLASH_ACR?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-21 06:05 AM

Prefetch buffer is enabled, when the fault occurs:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-22 07:23 AM

no more ideas here, sorry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-24 06:02 AM

Today I reproduced the issue on the STM32F3DISCOVERY-Board. The external clock is provided by aDSC6003JI2A-0000 connected to PF0-OSC_IN. The behavior is the same as with the custom hardware.

All project files are attached.

________________ Attachments : ExtClkTest.zip : https://st--c.eu10.content.force.com/sfc/dist/version/download/?oid=00Db0000000YtG6&ids=0680X000006HxZF&d=%2Fa%2F0X0000000azy%2F7gPD8cbRb9oQ8WY_haylHQsnnKhA8i1g4nAvLi4zn58&asPdf=false- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-01 03:10 AM

Hi Moritz,

Yes you are right the Flash latency should be calculated based on SYSCLK for the F3 series.

It will be fixed in the 4.26.1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-02 04:43 AM

GHARBI.Nawres

,The RM clearly states that latency is based on HCLK:

Are you suggesting, that a serious error in RM (and, presumably, in other 'F3xx RMs) is to be fixed in CubeMX???

Jan Waclawek

- STM32 setting AHB clock speed goes into infinite loop in HAL_RCC_ClockConfig in STM32 MCUs Embedded software

- STM32U5 hspi fifo in STM32 MCUs Products

- STM32H753VITx with ULPI USB3320 - corrupted data? in STM32 MCUs Products

- Display output does not appear when the start address is in SDRAM in STM32 MCUs Products

- Problem with PSRAM peripherals of STM32H735 in STM32 MCUs Products