- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- why is there a delay between (DR register written)...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

why is there a delay between (DR register written) and (data really showed) in UART on STM32F103CB?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-23 11:15 PM

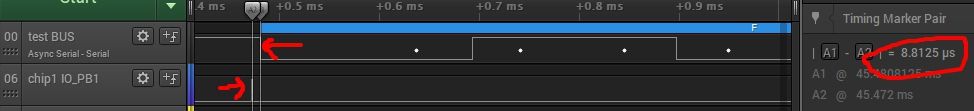

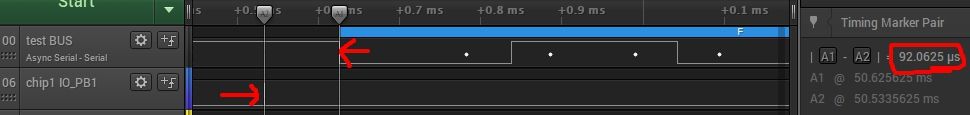

I'm curious about the delay time between the title mentioned, I toggled an IO when I wrote data into UART->DR, the delay time varies from 3 micro seconds to 10x micro seconds

int main(void)

{

/* initial code generated by STMCubeMX */

HAL_Init();

SystemClock_Config();

MX_GPIO_Init();

MX_USART1_UART_Init();

while (1)

{

HAL_Delay(50);

if (USART_GetFlagStatus(&huart1, USART_SR_TXE) == SET)

{

USART_SendData(&huart1, 'F');

}

}

}

void USART_SendData(UART_HandleTypeDef *huart, uint16_t Data)

{

assert_param(IS_USART_ALL_PERIPH(USARTx));

assert_param(IS_USART_DATA(Data));

GPIOB->BSRR = GPIO_PIN_1; // Tick an IO pin for debugging

GPIOB->BSRR = (uint32_t)GPIO_PIN_1 << 16u; // reset pin

huart->Instance->DR = (uint8_t)(Data & (uint8_t)0x00FF); // send data (write DR)

}I'm not sure whether the time jitters is related with BAUD rate 9600(104 micro seconds/bit),

Isn't the data should be showed immediately when DR register written????

And why isn't the delay time all the same(or close)?

Solved! Go to Solution.

- Labels:

-

Interrupt

-

STM32F1 Series

-

TIM

-

UART-USART

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-24 4:47 AM

I think the shift register is clocked by the baud rate generator. So the transfer from the DR to the shift register is clocked by the baud rate generartor not the bus clock.

Hence the delay from 0 to 1 bit time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-24 2:34 AM

USART transmission involve 2 registers; TDR and a hiden shift register.

When you write your first data to DR,

- The DR content is immediately transferred to the shift register

- The data begins to shift out of the TX pin

- The DR register becomes free and generate TXE

So the delay you measure is very small.

When you write your second data to DR the shift register is already full, and the DR register will be empty (and generete TXE) only at the end of the 1st data transfer.

So the delay you measure is near the transmission delay of 1 data.

Try to set the HAL_delay to more than 104 us.

You can think of the DR register as a 1-data FIFO!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-24 3:00 AM

@Nikita91 Thanks for reply

HAL_delay(50) delays 50 millisecond

Do you know the time and process of the data begins to shift out of the TX pin???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-24 3:37 AM

Sorry for the 50ms!

I don't know the delay.

The only thing I get from the RM is "An idle frame will be sent after the TE bit is enabled" (page 792/794 of RM008 rev 17).

So I understand that the delay of the first data may be different from the others.

I do not see anything else.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-24 4:47 AM

I think the shift register is clocked by the baud rate generator. So the transfer from the DR to the shift register is clocked by the baud rate generartor not the bus clock.

Hence the delay from 0 to 1 bit time.

- RTC not working on Vbat in STM32 MCUs Products

- Facing difficulties in interfacing STM32L433 MCU to VCNL4040 (I2C-based sensor). in Others: STM32 MCUs related

- What is the best PLL configuration for H533 ? in STM32 MCUs Products

- stm32U585 + 2 x APS25608N OSPI - speed problems in STM32 MCUs Products

- STM32H7 USART FIFO + character match: CMF not set until FIFO is actually read? in STM32 MCUs Products