- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- What is the most reliable way for clocking multipl...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the most reliable way for clocking multiple devices

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 11:15 AM

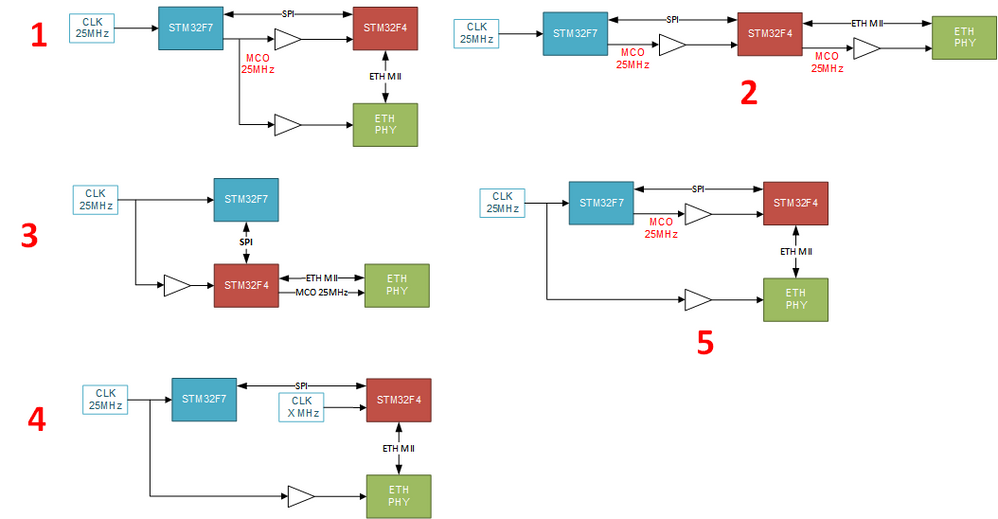

I have a SMT32F7 for control one STM32F4 for comms (ETH MII) and the ETH PHY and I was thinking either one of these (Inclining for number 3):

But I'm not an expert and would like to know what is the most reliable of these:

Or should I use 3 different clocks?

Thank for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 11:24 AM

What nature is the CLK 25MHz? Crystal or oscillator?

If oscillator, a solution no. 6 when all devices are supplied from the oscillator - most stable and least jitter.

If crystal, I'd prefer no. 2 - the F4 can stop or restart the PHY. Anyway, if precise clock fails, ETH won't work too reliably.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 11:27 AM

If CLK 25MHZ is a TCXO, option 6, buffer the same clock into all three.

Do you want to control the clocks going into the STM32F4 and ETHPHY? ie turn on/off, low power

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 11:32 AM

That's great! Both agree on number 6 independently.

That's the way I'll go.

Thanks so much for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 1:28 PM

snap

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 1:29 PM

Hi Edison, Is an oscillator (MEMS probably, still working on the design)

Thanks for your reply. Do you think I need 2 or 3 buffers for splitting the clock for your solution?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-05 1:30 PM

Hi Clive, No I don't need to.

Thanks

- STM32H503 simultaneous ADC and DAC use in STM32 MCUs Products

- Problem with UART Idle Line DMA Reception on STM32H563 Microcontroller in STM32 MCUs Products

- Same TouchGFX project for multiple CubeMX files in the same CubeIDE project in STM32 MCUs TouchGFX and GUI

- Advice on SPI and DMA for 24bit data on STM32H723 in STM32 MCUs Embedded software

- Hard faults, but not really == impossible to debug in STM32 MCUs Embedded software