- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Timer compare function interrupt not triggered som...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timer compare function interrupt not triggered sometimes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-10 6:44 PM

Hi everyone, I meet a problem and I'm not sure it's MCU issue or I program not proper.

I meet this issue both on the STM8 and STM32 MCUs.

I enable TIM_2 Ch1 as input to capture the signal and TIM_2 Ch2 as output to do the compare function.

void init_TIM_2

{

RCC.APB1ENR.bit.TIM2EN = 1;

..

TIM2.CCMR1.bit.Inmode.IC1S = 1;

TIM2.CCMR1.bit.Inmode.IC1PSC = 0;

TIM2.CCER.bit.CC1P = 0;

TIM2.CCER.bit.CC1E = 1;

..

TIM2.CCMR1.bit.Outmode.OC2S = 0;

TIM2.CCER.bit.CC2E = 1;

TIM2.DIER.bit.CC2IE = 1;

..

}

Also I enable the global interrupt with the NVIC module. So the interrupt is working.

And what I do in the interrupt just set a new compare value and toggle an GPIO pin.

void TIM2_ISR(void)

{

if (TIM2.SR.bit.CC2IF)

{

int p = TIM2_CCR;

int new_val = 0;

..

// Calculate a new compare value

// Toggle the GPIO pin

..

TIM2.CCR = p + new_val;

TIM2.SR.bit.CC2IF = 0;

}

}

I found it will miss the compare value sometime.

I trace the CCR value and timer counter value of TIM2, the CCR value should be greater than the counter value in normal case. But I found it's not triggered the ISR and the counter just exceed the CCR value sometimes.

If I program not proper, please have some advise for me. Thank you!

The actual data trace list as below:

| TIM2 CCR value | TIM2 counter value | Notes |

| 21735563 | 21729923 | |

| 21735563 | 21735024 | |

| 21735563 | 21740124 | The counter val > CCR and no interrupt event |

| 21735563 | 21745225 |

Solved! Go to Solution.

- Labels:

-

Interrupt

-

STM32F3 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-12 11:30 PM

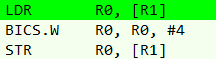

@waclawek.jan It really helps me a lot. I thought what I set is only 1 bit not a whole bits of register. But I trace the assembly code and it really did the LDR->BIC->STR and it cause the other interrupt flags clear either.

Many thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-14 12:38 AM

The reasons why for register accesses the bit-fields are harmful and useless:

- If one omits the volatile qualifier, the code is just broken.

- With the volatile qualifier every bit or bit-field access leads to a separate set of RMW instructions, which leads to a generally inefficient and for some uses (interrupt clearing) again broken code.

- « Previous

-

- 1

- 2

- Next »

- STM32WL3x Project Startup File Contains Incorrect Symbol Names for STMCubeMX Generated Project IRQ Handlers in STM32CubeMX (MCUs)

- H7: vector table in ITCM, jump app <-> bootloader in STM32 MCUs Products

- Maximizing USB Full-Speed CDC Data Rates on Dual-Core STM32WB55 in STM32 MCUs Wireless

- Ask for I3C support on NUCLEO-H563ZI (MB1404C) in STM32 MCUs Embedded software

- CCID USBD transfer block on F1 in STM32 MCUs Embedded software