- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: This can be realized with DAC and ADC in STM32...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

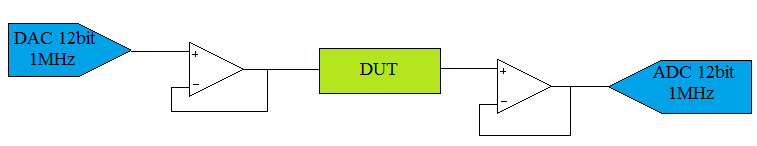

This can be realized with DAC and ADC in STM32F103?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-01 07:52 AM

Rapid

insight into

the datasheet

no problem

,

but

rather

ask:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-01 08:57 AM

I looks plausible, just, for a 72 MHz F1, there are likely better choices to get a more stable 1MSps

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-01 11:34 AM

I thought about

STM32F103RD on 56MHz, Rdue to 64kB RAM and 56MHz

because

max ADC fadc is 14MHz.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-01 11:18 PM

> This can be realized with DAC and ADC in STM32F103?

In theory, yes. However, ST's DAC implementation has settling rates of about 4 .. 5 us (check the datasheet), you will hit a bandwidth limit here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-02 01:43 AM

The devil is in the details.

In datasheet say t setting =3-4us Settling time (full scale: for a 10-bit input code transition between the lowest and the highest input codes when DAC_OUT reaches final value ±1LSB.Expressed in angles, Setting from 0 to 1/2PI and for load R=5kOhm C=50pF. For my sinus wave have transition 250 point to 1/2PiIf use external amplifier for example AD8628 total setting time =Sqrt(tsDAC^2 +tsAMP^2)= Sqrt (4^2+3.3^2)=5.2us max and 4.5us Typ, for code transition from 0 to 4096, 5.2/4096 = 1.27ns/LSB. Biggest change in my sinus wave is 13LSB 16.5ns.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-02 03:27 AM

> The devil is in the details.

Yes, you need to check it for your own application. Just wanted point out the fact that you can feed the DAC DR register much faster than the output can follow. A 3db-bandwidth of 1.0 MHz (or 500kHz) is unrealistic.

- CubeMX and CubeIDE interaction - User Code being overwritten in STM32 MCUs Products

- PWM Capture with EXTI Interrupts: Eliminating Noise Spikes in STM32 MCUs Products

- Can't receive data on UART7 in STM32H7S78-DK while using UART4 in STM32 MCUs Boards and hardware tools

- Pull-up and Pull-down resistors in STM32 microcontrollers in STM32 MCUs Products

- OpenOCD does not bypass data cache in STM32 MCUs Embedded software