- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32L486 mcu used as Master SPI, Zigbee devic...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32L486 mcu used as Master SPI, Zigbee device as slave. What configuration of SSM and SSI should i be using?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 03:30 AM

I am going through an existing implementation, where my MCU's(STM32L486) SPI1 (PA4(NSS), PA5(SCK), PA6(MISO), PA7(MOSI) is used as master, the slave device is a zigbee stack.

Currently the master's SSL is configured as Software managed, (SSM=1, SSI= 1).

But the slave expect it to be asserted/deasserted through its SSL pin externally (GPIO).

In this case can i use the PA4(NSS) pin of the master to select the slave. this pin is connected to the SSL of slave.

My doubt is although the master is configured for software slave management, can it drive its PA4(NSS) pin for controlling the slave, Is this configuration correct or can cause problem?

- Labels:

-

SPI

-

STM32L4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 05:39 AM

The STM32 NSS pin controlled by SW (even not an alternate function) will be more than enough, especially because Zigbee are probably not bandwisth demanding. In this case, the SPI HW NSS signal is not going out of the chip, and that's my typical way. As such, any pin of the STM32 can be used. brings some degrees of freedoom in the pin selection.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 06:01 AM

the content is in reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 06:07 AM

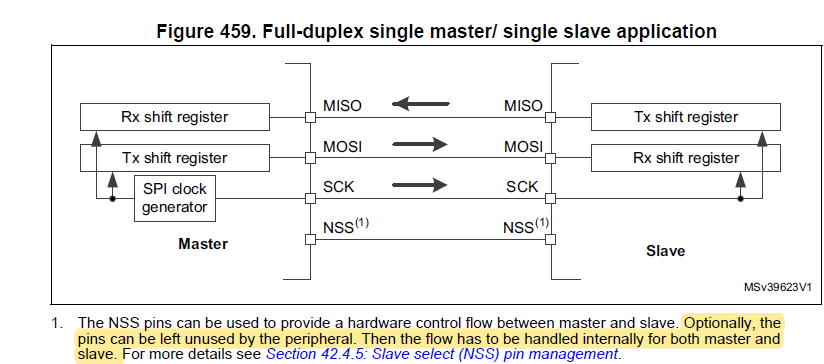

"Optionally, the pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and slave"

Here it is mentioned "then the flow has to be handled internally for both master and slave".

Which puts a question in my mind that either both slave and master use internal bits for their SSL configuration

OR

if Slave is not configured using internal SSL configuration, use an explicit GPIO pin.

Please correct my understanding.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 06:16 AM

Thanks for the reply ... i havent picked up all the things u mentioned.

"In this case, the SPI HW NSS signal is not going out of the chip" -> do you mean

Because of the specific configuration of master (SSM = 1 and SSI = 1), the NSS signal doesnt generate any signal at the NSS pin level, so i cant connect this to slave's SSL pin. So i should use some other GPIO

OR

i can drive the PA4(NSS) pin using HAL GPIO API, and this will not cause any side effects.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 06:37 AM

The peripheral and its signals can be routed to GPIO through the alternate functions... or not.

So you should just select any GPIO as push pull output and drive it by SW to become the master's NSS.

The peripheral guts is like the brain without all nerves connected to muscles...

The drawing Figure 459 is misleading as it simply says if you know what you are doing and you don't need to get NSS to tell you the start and end of message, then you can forget it, which is rarely the case: a simple bus glitch and all your data maybe few bits shifted... and what happens if the slave is reset or the master is separately reset? boum!

You can set the SPI as you said, and not activate the alternate function to let the signal out. Then use the corresponding GPIO simple Set/Reset output level to generate the NSS. Use PA5 (or any pin you wish) as push pull output (mode=01) to generate the NSS for the slave.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 07:24 AM

I believe you meant PA4(NSS pin) of the master can be used to drive the slave select low and high without any side effects although master has Software slave management enabled.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 07:40 AM

Correct.

- I2C 16x2 Led Display. Problems in driving it. Please help. in STM32CubeIDE (MCUs)

- UART DMA &SPI DMA and Semaphore Mutex issue in STM32 MCUs Products

- CAN1 RX issue in STM32 MCUs Products

- Low consumption NucleoL476RG in STM32 MCUs Boards and hardware tools

- Weird horizontal artifacts in touchGFX buttons in STM32 MCUs TouchGFX and GUI