- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32H735RGV6 ADC Dual Interleaved Mode Single DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H735RGV6 ADC Dual Interleaved Mode Single DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-21 5:00 AM

Hello Sir/Madam,

I am working on STM32H735RGV6 for interleaved mode single dma. I am having problems while getting samples from the DMA controller with ADC. The problem is as the following.

1. If I want to get 8192 or a smaller number of samples, there is no problem. I am getting the whole sample.

2. If I want to get 8193 or greater samples, then a DMA transfer error occurs.

The following pictures show my setup for ADC1 and ADC2.

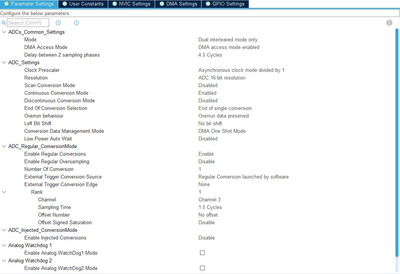

ADC 1 settings

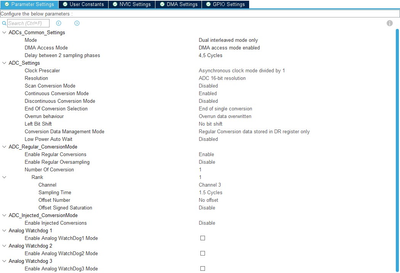

ADC 2 settings

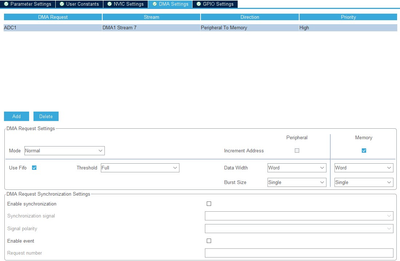

ADC 1 DMA settings

#define ADC_DMA_BUFFER_SIZE (16384)

volatile __attribute__((section(".dma_buffer_ram2"))) uint16_t ui16pAdcBuffer[ADC_DMA_BUFFER_SIZE];

ui16pAdcBuffer --> It is in RAM_D2

ADC DMA calling function setup 1: the following setup works well many times without any problem and I am getting HAL_ADC_ConvCpltCallback each time I want samples from ADC

ui32AdcDataSize = 8192

if(HAL_ADCEx_MultiModeStart_DMA(&hadc1, (uint32_t*)ui16pAdcBuffer, ui32AdcDataSize) != HAL_OK)

{

Error_Handler();

}

ADC DMA calling function setup 2: the following setup is not working. When I want 8193 samples from ADC I am getting ADC_DMAError and HAL_ADC_ConvCpltCallback is not called.

ui32AdcDataSize = 8193

if(HAL_ADCEx_MultiModeStart_DMA(&hadc1, (uint32_t*)ui16pAdcBuffer, ui32AdcDataSize) != HAL_OK)

{

Error_Handler();

}

The number 8192 is somehow interesting. Likely, it tells me that there can be a limit on ADC-DMA but I am not sure about it.

Could you help me with this issue?

Best regards,

Ersin

Solved! Go to Solution.

- Labels:

-

ADC

-

DMA

-

STM32H7 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-21 12:32 PM

Hello @Ersin Kuscu

The maximum length of data to be transferred from ADC peripheral to memory should be in 256 x32 =8192.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-21 12:32 PM

Hello @Ersin Kuscu

The maximum length of data to be transferred from ADC peripheral to memory should be in 256 x32 =8192.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-22 3:04 PM

Hello @FBL ,

Thank you for your answer.

Could you share where I can find that information?

Best regards

Ersin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-06-23 8:18 AM

Hello @Ersin Kuscu

The transfer size is defined by the DMA_SxNDTR register value and by the peripheral side (ADC1) data width.

According to the reference manual, a stream has an independent 4-word (4 * 32 bits) FIFO.

To ensure that the last burst transfer is not incomplete, the total number of data items must be multiple of the burst size multiplied by the data size.

For more details, you can either check the reference manual 15.3.12 Programmable data width, packing/unpacking, endianness, or Using the STM32F2, STM32F4 and STM32F7 Series DMA controller

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- WebSocket Server on STM32H7xx with Azure RTOS and NetXDuo — A Practical Guide in STM32 MCUs Embedded software

- STM32H735G-DK: MDMA Linked List Transfer Causing Choppy ADC Output to HyperRAM in STM32 MCUs Embedded software

- STM32 Design Review in Others: STM32 MCUs related

- STM32F103C8T6 does not transmit or receive on UART2 in half duplex in STM32 MCUs Embedded software

- ADC1 and 2 dual (interleaved) mode, differential and fast channels in STM32 MCUs Products