- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32H7: SPI problem with SPI_RXDR

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H7: SPI problem with SPI_RXDR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2025-01-28 03:32 AM

I am using the STM32H725RE (68-pin package).

My goal is to have full duplex SPI communication with a 16 bit shift register using the stm32h7 as the SPI master (with no dma controller).

I am using the SPI3 with the following pin (12MHz)

PA15 (SPI3_nCS), PC10 (SPI3_SCK), PC11 (SPI3_MISO) and PC12 (SPI3_MOSI).

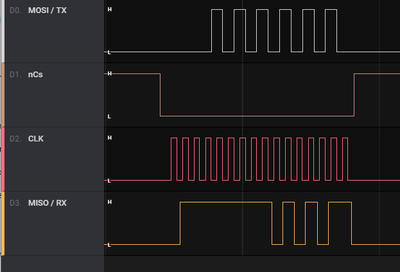

With the following code it is already possible to write the data successfully and the shift register also sends the data correctly to the MISO wire. (as you can see in the logic analyser screenshot)

But I have problems reading the receive buffer, the flags are set correctly (RXP is set correctly), but when I read the RXDR I only read the data 0xFFFF, although other data should be read as shown in the logic analyser screenshot?

- Labels:

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2025-01-28 03:59 AM

Did you check with a scope that RX really is available at the pin? Did you check for other hardware errors/misshaps?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2025-01-28 04:22 AM

I am using a logic analyser and I have seen that data is also being sent on the miso line, see screenshot in the main post.

- Problems controlling SK6812RGBW/Neopixel with STM32H7 in STM32 MCUs Products

- SDMMC IDMA double buffer mode multi-block write stops before expectation in STM32 MCUs Boards and hardware tools

- STM32H725 SMPS issue in STM32CubeMX (MCUs)

- Issue with srand() causing exit in STM32H747 Project with FreeRTOS and lwIP in STM32 MCUs Embedded software