- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G474: Descriptions on access paths to SRAM2 i...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G474: Descriptions on access paths to SRAM2 is inconsistent within a data sheet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-07 1:27 AM

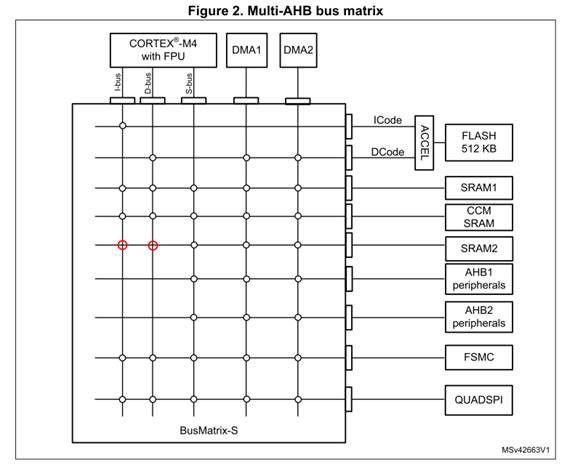

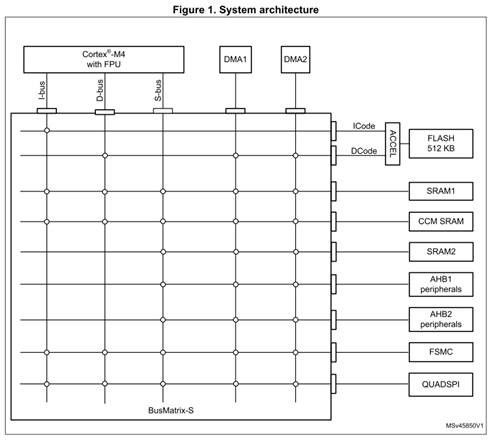

DS12589 Rev 1 (for G431) and DS12288 Rev 1 (for G474) both states in Section 3.5 that SRAM2 can be accessed by CM4 core through System Bus or through the I-Code/D-Code bus. However, Figure 2 "Multi-AHB bus matrix" suggests that SRAM is only accessible by CM4 core through System Bus.

- Labels:

-

Documentation

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-07 1:38 PM

That's most probably a copy/paste error, there's no indication that SRAM2 could be remapped to the I/D address space.

JW

@Imen DAHMEN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-11 12:10 AM

Hello,

We will correct the figure in the coming release of datasheets :

The SRAM2 can be accessed by the CPU I-bus and D-bus after remap (like SRAM1). SRAM2 is supplied independently and can be retained in Standby mode.

Thanks for bringing this typo to our attention.

Best Regards,

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-11 2:06 AM

Hi Imen ,

Thanks for the clarification.

> after remap (like SRAM1).

How exactly? Does it remap together with SRAM1, as its continuation; or does it remap separately being mapped onto 0x00000000?

I grab on the oportunity and abuse this thread to ask a related question (I keep asking here for years) for the 'F4 family: RM0090 rev.17 ([edit] and also rev.18[/edit]) in chapter 2.3.1 Embedded SRAM says:

The CPU can access the SRAM1, SRAM2, and SRAM3 through the System Bus or through

the I-Code/D-Code buses when boot from SRAM is selected or when physical remap is

selected

However, exactly as here in the case of 'G4, there is no indication in the bus matrix diagrams, the Memory mapping vs. Boot mode/physical remap tables, nor in SYSCFG_MEMRMP.MEM_MODE description, that SRAM2 (and SRAM3 for the 'F42x/'F43x) could be remapped.

Can ST please clarify?

Thanks,

Jan

@Imen DAHMEN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-30 2:16 AM

Hello Jan,

Sorry, after deep check, the original picture is correct and we will modify the description in the documents.

The SRAM2 is not accessible through I/D bus. The remap is possible only for SRAM1 / FMC / QUADSPI and the Flash.

Kind Regards,

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-30 3:38 AM

Hi @Imen DAHMEN ,

thanks for the clarification.

Can please wording of chapter 2.3.1 Embedded SRAM in RM0090 be fixed accordingly, too?

Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-30 6:52 AM

Hi @Community member ,

Yes, I also raised this typo internally for correction in the coming release of RM0090.

Many thanks for bringing this to our attention.

Best Regards,

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-30 8:54 AM

Thanks, Imen.

Jan

- STM32U575 TrustZone Proect Interrupt Confusion in STM32 MCUs Embedded software

- Inconsistency in WWDG_CFR description for STM32G0xx and STM32C0xx in STM32 MCUs Products

- STM32G474 HAL_TIM_Encoder_Start_DMA Question in STM32 MCUs Products

- Is UM1884 (STM32L4/L4+ HAL and low-layer drivers UM) description for RCC_PLLInitTypeDef inconsistent with header file 'stm32l4xx_hal_rcc.h' generated by STM32CUBEMX with respect to PLLP, PLLR parameter definitions? in STM32 MCUs Embedded software

- Setting VREF voltage in CubeMX not working correctly for STM32H7 in STM32CubeMX (MCUs)