- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F746 timer generated trigger for ext. ADC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F746 timer generated trigger for ext. ADC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 02:33 AM

Dear STM32 timer specialists,

i have to design a board, where a STM32F746 must read a 16 bit/40MSample ADC, into internal or external (SD)RAM. The ADC data bus will be 32 bit wide with 20MHz clock. The memory interface is an other problem, but i have to generate 3 different trigger signal for the ADC (it is 1 trigger signal, for 3 different configurations, to read 1, 2 or 3 channels). I have attached the timing diagram from the ADC datasheet.

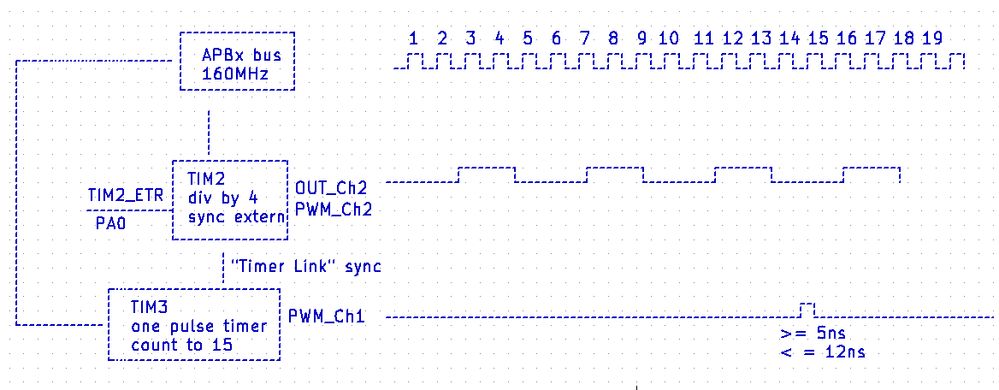

My problem is now the question: can the trigger signal be generated by the STM32F746 timers, or do i need external logic to generate them. If possible, i would prefer the STM32F746 internal timer, to save board space and cost. Further would it be great if the sync-to-external-ref-clock feature of the STM32 timer could be used. After reading the STM32F746 datasheet and the 'STM32 timer cookbook', i think the following setup should work(ADC_triggerGen_STM32F746_3ch.png):

- APB1/2 bus setup for 200MHz

- TIM2 with the ETR2(sync in) and OUT_CH2(or PWM_CH2) as MCLK for the ADC

- --- TIM2 should divide the APBx frequency divide by 5 to output 40MHz

- Ether TIM6,7,8,10,11 or 13 to count to 13(8,5) to generate the signal for the 3 channel(2 channel, 1 channel) trigger

- TIM1 configured as one pulse timer, triggered by the above TIM(6,7,8,10,11 or 13) and ouput on PWM_CH1.This one pulse generator is needed to create the trigger pulse according the timing diagram of the ADC, it must be min. 5ns and max. 12.5ns.

- 3 hardware pins used (ETR2, OUT_CH2, PWM_CH1)

This setup should work just in hardware, without CPU load if possible (except the setup and switching between 1channel, 2 channel or 3 channel mode).

The timing restrictions in timing_3ch_detail.png:

tPER min=25ns (MCLK period)

tMCLKH typ=0.5tPER (MCLK high period )

tMCLKL typ=0.5tPER (MCLK low period )

tMRVSR min=3ns (MCLK rising to VSMP rising time)

tVSD min=2ns (VSMP pulse high time)

tMFVSF min=7ns (MCLK falling to VSMP falling time)

MRVSR min=3ns (MCLK rising to VSMP rising time)

Would be great, if someone could confirm, that this hardware setup can generate the required timing. Or hint me on possible limitations of the used timers. Then i could finalize the hardware part.

Thank you in advance for your help.

#stm32f746 #timer-triggered-adc- Labels:

-

STM32F7 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 03:17 AM

'

can the trigger signal be generated by the STM32F746 timers, or do i need external logic to generate them.'

yes and no, depending on which of the two timing parameters cited by you is true.

if you are sampling at 40MSPS, you likely have exceeded the chip's capability - check the spi module for sure.

if you are sampling at 32-bit 20Mhz, you are essentially sampling the adc at 5MSPS, and it shouldn't be a problem for the adc/mcu.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 06:42 AM

dear dhenry,

first, thanks for looking on my problem. You say '

yes and no, depending on which of the two timing parameters cited by you is true.

' What you mean with 'two timing parameters'? You mean the TIM2 for the 40MHz MCLK is possible, but the TIM6 + TIM1 combo for the trigger pulse not?Maybe my writing was a bit confusing, because i asked for all 3 modes i like to implement. To make it easier to understand, let me just ask for the 3 channel mode, what is the most needed.

- APB1/2 bus setup for 200MHz

- TIM2 with the OUT_CH2(or PWM_CH2) as MCLK output for the ADC

- --- TIM2 should divide the APBx frequency divide by 5 to output 40MHz ADC-MCLK

- TIM6 (feed by 200MHz APBx) to count to 13 to generate the signal for TIM1

- TIM1 configured as one pulse timer, triggered by the above TIM6 and output on PWM_CH1(=ADC-TRIGGER). This one pulse generator is needed to create the trigger pulse according the timing diagram of the ADC, it must be min. 5ns and max. 12.5ns.

Can ADC-MCLK be generated by TIM2? Can ADC-TRIGGER be generated by TIM6+TIM1?

------------------------------------------------

The ADC is a 16 bit / 40 MSamples per second ADC, with a 8bit, 80MHz parallel interface, what i like to widen to 32 bit / 20MHz(with 2 * 74xx16373 latch). That is 80 Mega Byte, ether 1 byte * 80MHz, or 2 byte * 40MHz or 4 byte * 20MHz. I was hoping that the FMC (flexible memory controller) could handle 32 bit * 20MHz, maybe with burst read and DMA. From the STM32F746 Reference Manual, a Memory transaction is [ADDSET + (DATAST+1)] HCLKs. If we set the FMC to 80MHz clock, ADDSET=1, DATAST=2, a read speed of 20MHz*32bit should be doable from those specs. Or did i miss something?

In a extreme, the ADC looks like a single 32 bit ROM address on the Databus, and the ADDSET can be set to 0. So the theoretical limit should be 40 million bus reads on the FMC? On the other hand, i must admit, that I not really understand the STM32F746 Reference Manual about the FMC:

13.5 NOR Flash/PSRAM controller:

Asynchronous SRAM and ROM: 8/16/32 bit supported

BUT in 13.5.2 Supported memories and transactions

'Table 61. NOR Flash/PSRAM: example of supported memories and transactions' only 16 bit Memory data size is shown. SRAM and ROM: AHB data size: 32 bit Memory data size: 16 bit Coment: Split into 2 FMC accesses.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 07:39 AM

- you can't divide by 5 'symmetrically' - the best you can achieve is 2:3 duty - your decision if this is OK

- you don't need additional timer to count pulses for the second waveform - one timer is enough, simply change its period

- what's the purpose of 'ETR2(sync in)'?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 07:43 AM

- you can't divide by 5 ''symmetrically'' - now where you say it, i see it as well. I thought, i can use a PWM timer setup with 50% duty cycle, but there are not enough clock cycles for a 50% duty PWM. Using 160MHz APB1 and divide by 4 to get the 40 MHz should be ok?

- what's the purpose of ''ETR2(sync in)''? I would like to be able to synchronize the ADC trigger to an external reference signal. As outlined in AN4776 ''STM32 timer cookbook'', chapter ''Timer clocking using external clock-source''. For now, i only ensure the pin (PA0 - TIM2_ETR) is brought out on the PCB.

I have updated the clock tree to 160MHz div 4:

Will it wok this way?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 11:07 AM

- you can't divide by 5 'symmetrically' - now where you say it, i see it as well. I thought, i can use a PWM timer setup with 50% duty cycle, but there are not enough clock cycles for a 50% duty PWM. Using 160MHz APB1 and divide by 4 to get the 40 MHz should be ok?

In fact, the assymetric waveform, while not typical, in most of the cases is OK too - that would require to be verified in the ADC's DS.

I don't believe you'd be able to sink those data from FMC through DMA. DMA has its overhead, read AN4031. You may want to have a closer look at DCMI.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 07:08 PM

Dear Jan,

thanks for your fast response and the patience to answer my questions. After seeing the limitations, i will go the route with an FPGA. The hint with the DCMI was good, but actually not within my requirements.

I am quite happy with the fast response in this forum, and the qualified answers. You saved me from a mis-concept.

- TIM_OCActive example, setting TIM1 CH1 output pin PA8 to HI is visible for all four channels in STM32 MCUs Products

- Generic-Switch-App: After restarting the device, button 2 cannot trigger automation in STM32 MCUs Wireless

- How to implement PLL in STM32? in STM32 MCUs Motor control

- External ADC Sampling with DMA (Timing & Configuration) in STM32 MCUs Products

- Changing scene in Model.cpp fails in STM32 MCUs TouchGFX and GUI