- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F746 Cortex-M7 silicon bug. Singlestep la...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F746 Cortex-M7 silicon bug. Singlestep lands in interrupt handler

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-10 6:09 AM

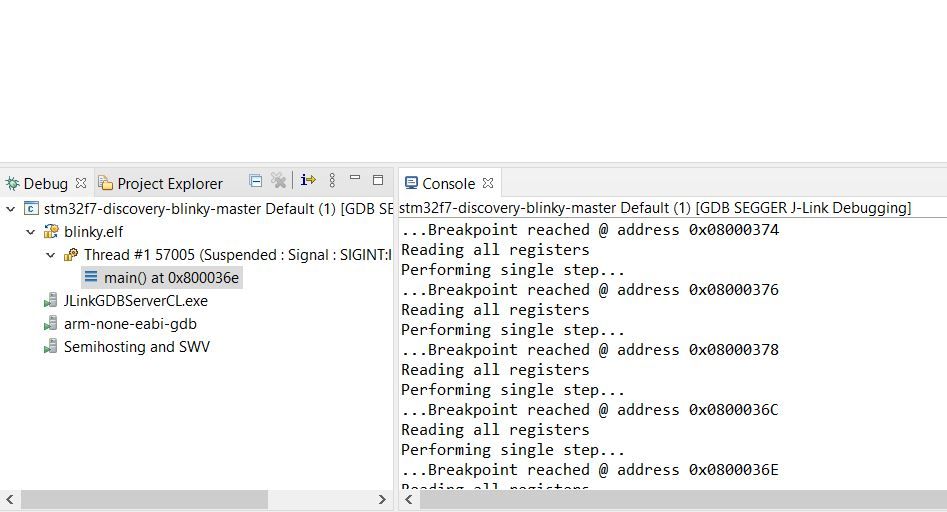

I'm running into the Cortex M7 r0p0, r0p1 bug where single-stepping is impossible due to the processor handling an interrupt instead.

i.e.

http://www.keil.com/support/docs/3778.htm

I'm using OpenOCD and it is reporting:

Warn : Silicon bug: single stepping will enter pending exception handler!

As per title, this is with an STM32F746Z on a Nucleo 144 which has the bug. STM32F769N worked as expected.

Are there any plans from ST to release a fixed ARM core in the 746 or 745?

regards

James

Solved! Go to Solution.

- Labels:

-

STM32F7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-10 7:23 AM

>>Are there any plans from ST to release a fixed ARM core in the 746 or 745?

This topic has been discussed before, and no, they don't plan on updating the core. The debugging case is a ppm/ppb use case, and doesn't impact product level functionality.

The F722 has a newer core, as do the F76x/77x and H7 parts.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-10 7:23 AM

>>Are there any plans from ST to release a fixed ARM core in the 746 or 745?

This topic has been discussed before, and no, they don't plan on updating the core. The debugging case is a ppm/ppb use case, and doesn't impact product level functionality.

The F722 has a newer core, as do the F76x/77x and H7 parts.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-10 8:35 AM

Thanks for the answer, I did try searching, but perhaps not hard enough.

Shame that the chip won't be fixed as it currently makes debugging very difficult.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-10 9:08 AM

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-19 5:38 PM

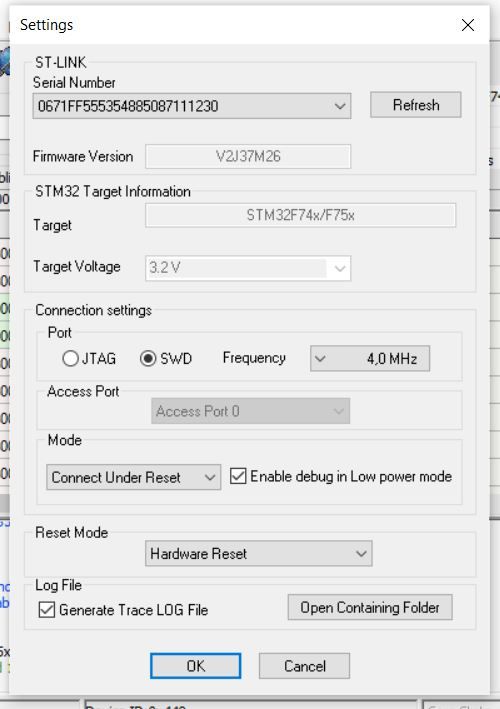

SEGGER have implemented a workaround for this hardware core bug in their J-Link debuggers. On-board ST-LINK can be converted to J-Link OB.

https://www.segger.com/products/debug-probes/j-link/models/other-j-links/st-link-on-board/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-15 5:59 PM

It does not work in Segger J-Link OB either...Seems once again ST Sold a $70 dollar board without single stepping ability so shifting blame to Segger is a poor implementation of a joke without re-spinning the Silicone...It only works by using the ST Link Utiliy in a special tweaked mode...Open OCD does not work using ST Link or upgrading to Segger. It cannot step as specified above...Single Stepping fails completely in Segger J-Link OB by jumping steps because it cannot stop on a breakpoint and runs hay-wire...Same deal with ST-Link...Sad as it looked like a promising board! Unfortunately it is Junk in any debug mode and I have tried them all...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-15 6:37 PM

It is an ARM issue, which they resolved in subsequent spins of their deliverable IP. ST was one of the first companies to get ARM CM7 silicon for them to work with.

ST isn't going to do-over the chip layout and validation, the design team(s) rotated into the next products, it is out of the design cycle, and into the fab/production cycle, and it will be there until end-of-life. Its not a process of constant introspection and correction of a design that's already left the factory.

If you really need to single step your code to understand flow/dynamics then you'll need to pick a part which is a close proxy or use more classical analysis methods.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-17 5:29 PM

Clive1 - I would love to agree with you but it is a sad manufactured crisis, the story that you concatenated for the unexpected core reset happening suddenly and very unacceptable. The code breaks fine on simple tasks till we get to audio codec work...Then it does not break at all...Do you Mind re-thinking your ugly explanation for selling a broken platform for mass production answer and blaming ARM and perhaps blaming it on work via Audio Codecs ? What IP are you guys protecting exactly and why ???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-18 3:48 PM

I have a workaround that allows me to use breakpoints on STM32F745 with the on-board STlink and OpenOCD.

When you hit the breakpoint:

Step

(lands in an interrupt)

Set Registers -> primask to 1

Run (seems like it didn't do anything)

Step

Continue stepping like normal.

But it is indeed a PITA.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-18 3:55 PM

Just to clarify, do you mean F76x/77x or F7x6/7x7 ?

The latter is more in line with the product page: https://www.st.com/en/microcontrollers-microprocessors/stm32f7-series.html (Which I find illogical, the sub-family number would make a lot more sense as the middle number not the final one.)

e.g. F746, F756, F767, F777

James

- Removing call to HAL_DAC_IRQHandler in TIM6_DAC_IRQHandler in STM32CubeMX (MCUs)

- TouchGFX with ThreadX using 10ms timer in STM32 MCUs Embedded software

- How to receive data from UART using STM32f746-Disco in STM32 MCUs Products

- HID host USB for getting barcode from a scanner. in STM32 MCUs Products

- Generated HAL Timer Tick generated code has an error - F7 in STM32CubeMX (MCUs)