- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F429 Communication with STM32F401 use SPI, th...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F429 Communication with STM32F401 use SPI, the slave data shift.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-17 1:04 AM

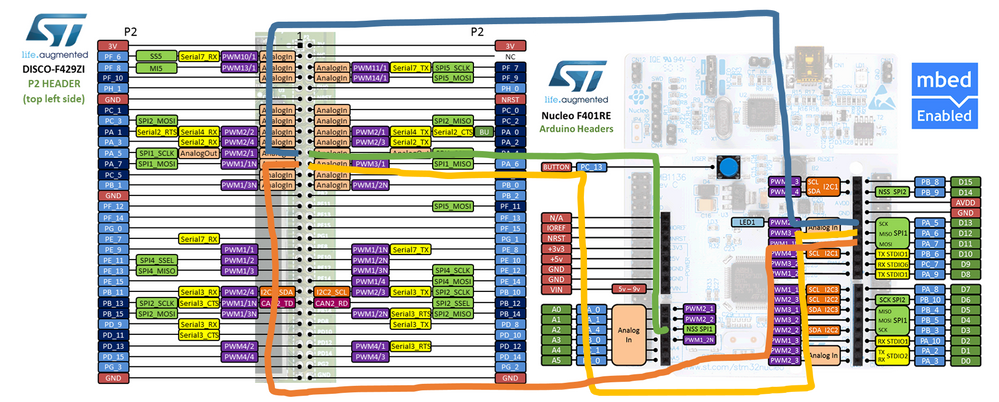

board: STM32F429I-DISC1

NUCLEO-F401RE

I use SPI with DMA , but the MOSI will shift randomly.

Connection of two boards.

Master(STM32F429)

void init_SPI1(void)

{

GPIO_InitTypeDef GPIO_InitStruct;

SPI_InitTypeDef SPI_InitStruct;

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1, ENABLE);

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_5| GPIO_Pin_6 | GPIO_Pin_7;

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF;

GPIO_InitStruct.GPIO_OType = GPIO_OType_PP;

GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_NOPULL;

GPIO_Init(GPIOA, &GPIO_InitStruct);

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_9 ;//Select Chip

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_OUT;

GPIO_InitStruct.GPIO_OType = GPIO_OType_PP;

GPIO_InitStruct.GPIO_Speed = GPIO_Speed_100MHz;

GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_UP;

GPIO_Init(GPIOD, &GPIO_InitStruct);

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_4 ;//Select Chip

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_OUT;

GPIO_InitStruct.GPIO_OType = GPIO_OType_PP;

GPIO_InitStruct.GPIO_Speed = GPIO_Speed_100MHz;

GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_UP;

GPIO_Init(GPIOA, &GPIO_InitStruct);

GPIO_SetBits(GPIOA, GPIO_Pin_4);//For stm32f429 discovery board

GPIO_SetBits(GPIOD, GPIO_Pin_9);//For stm32f401 manual board

GPIO_PinAFConfig(GPIOA, GPIO_PinSource5, GPIO_AF_SPI1);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource6, GPIO_AF_SPI1);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_SPI1);

SPI_I2S_DeInit(SPI1);

SPI_InitStruct.SPI_Direction = SPI_Direction_2Lines_FullDuplex;

SPI_InitStruct.SPI_Mode = SPI_Mode_Master;

SPI_InitStruct.SPI_DataSize = SPI_DataSize_16b;

SPI_InitStruct.SPI_CPOL = SPI_CPOL_High;

SPI_InitStruct.SPI_CPHA = SPI_CPHA_1Edge;

SPI_InitStruct.SPI_NSS = SPI_NSS_Soft|SPI_NSSInternalSoft_Set ;

SPI_InitStruct.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_8 ;

SPI_InitStruct.SPI_FirstBit = SPI_FirstBit_MSB;

SPI_InitStruct.SPI_CRCPolynomial = 7;

SPI_Init(SPI1, &SPI_InitStruct);

SPI_I2S_ITConfig(SPI1, SPI_I2S_IT_RXNE, ENABLE);

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_InitStructure.NVIC_IRQChannel = SPI1_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelCmd = DISABLE;

NVIC_Init(&NVIC_InitStructure);

SPI_Cmd(SPI1, ENABLE);

}

void Finger_Connect(uint16_t mode)

{

GPIO_ResetBits(GPIOA, GPIO_Pin_4);

GPIO_ResetBits(GPIOD, GPIO_Pin_9);

while(SPI_I2S_GetFlagStatus(SPI1,SPI_I2S_FLAG_TXE) == RESET);

SPI_I2S_SendData(SPI1,mode);

while(SPI_I2S_GetFlagStatus(SPI1, SPI_I2S_FLAG_RXNE) == RESET);

SPI_Buffer_Rx[0] = SPI_I2S_ReceiveData(SPI1);

for(int i = 0 ; i <spirecivetime ; i++){

while(SPI_I2S_GetFlagStatus(SPI1,SPI_I2S_FLAG_TXE) == RESET);

SPI_I2S_SendData(SPI1,0xAAAA);

while(SPI_I2S_GetFlagStatus(SPI1, SPI_I2S_FLAG_RXNE) == RESET);

SPI_Buffer_Rx[i+1] = SPI_I2S_ReceiveData(SPI1);

}

GPIO_SetBits(GPIOA, GPIO_Pin_4);

GPIO_SetBits(GPIOD, GPIO_Pin_9);

}Slave(STM32F401)

uint16_t SEND_BUFF[15]={0x5555,0xAAAA,0x1234,0x2345,0x3456,0x4567,0x5678,0x6789,0,0,0,0,0,0,0}, RECEIVE_BUFF[15]={0};

void init_SPI1(void)

{

GPIO_InitTypeDef GPIO_InitStruct;

SPI_InitTypeDef SPI_InitStruct;

DMA_InitTypeDef DMA_InitStructure;

NVIC_InitTypeDef NVIC_InitStructure;

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA, ENABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1, ENABLE);

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_DMA2, ENABLE);

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_4| GPIO_Pin_5| GPIO_Pin_6 | GPIO_Pin_7;

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF;

GPIO_InitStruct.GPIO_OType = GPIO_OType_PP;

GPIO_InitStruct.GPIO_Speed = GPIO_Speed_100MHz;

GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_NOPULL;

GPIO_Init(GPIOA, &GPIO_InitStruct);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource4, GPIO_AF_SPI1);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource5, GPIO_AF_SPI1);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource6, GPIO_AF_SPI1);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource7, GPIO_AF_SPI1);

SPI_I2S_DeInit(SPI1);

SPI_InitStruct.SPI_Direction = SPI_Direction_2Lines_FullDuplex;

SPI_InitStruct.SPI_Mode = SPI_Mode_Slave;

SPI_InitStruct.SPI_DataSize = SPI_DataSize_16b;

SPI_InitStruct.SPI_CPOL = SPI_CPOL_High;

SPI_InitStruct.SPI_CPHA = SPI_CPHA_1Edge;

SPI_InitStruct.SPI_NSS = SPI_NSS_Hard ;

SPI_InitStruct.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_2;

SPI_InitStruct.SPI_FirstBit = SPI_FirstBit_MSB;

SPI_InitStruct.SPI_CRCPolynomial = 7;

SPI_Init(SPI1, &SPI_InitStruct);

/* SPI_MASTER_Rx_DMA_Channel configuration ---------------------------------*/

DMA_DeInit(DMA2_Stream2);

DMA_DeInit(DMA2_Stream5);

DMA_StructInit(&DMA_InitStructure);

DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)(&(SPI1->DR));

DMA_InitStructure.DMA_BufferSize = SPI_BUFFERSIZE;

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;

DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_HalfWord;

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_HalfWord;

DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;

DMA_InitStructure.DMA_Priority = DMA_Priority_High;

DMA_InitStructure.DMA_FIFOMode = DMA_FIFOMode_Disable;

DMA_InitStructure.DMA_FIFOThreshold = DMA_FIFOThreshold_1QuarterFull ;

DMA_InitStructure.DMA_MemoryBurst = DMA_MemoryBurst_Single ;

/* SPI_MASTER_Rx_DMA_Channel configuration ---------------------------------*/

DMA_InitStructure.DMA_Channel = DMA_Channel_3;

DMA_InitStructure.DMA_Mode = DMA_Mode_Circular;

DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)RECEIVE_BUFF;

DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralToMemory;

DMA_Init(DMA2_Stream2, &DMA_InitStructure);

DMA_Cmd(DMA2_Stream2, DISABLE);

/* SPI_MASTER_Tx_DMA_Channel configuration ---------------------------------*/

DMA_InitStructure.DMA_Channel = DMA_Channel_3;

DMA_InitStructure.DMA_Mode = DMA_Mode_Circular;

DMA_InitStructure.DMA_Memory0BaseAddr = (uint32_t)SEND_BUFF;

DMA_InitStructure.DMA_DIR = DMA_DIR_MemoryToPeripheral;

DMA_Init(DMA2_Stream5, &DMA_InitStructure);

DMA_Cmd(DMA2_Stream5, DISABLE);

NVIC_InitStructure.NVIC_IRQChannel = DMA2_Stream5_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

NVIC_InitStructure.NVIC_IRQChannel = DMA2_Stream2_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

DMA_ClearFlag(DMA2_Stream2, DMA_FLAG_TCIF2);

DMA_ClearFlag(DMA2_Stream5, DMA_FLAG_TCIF5);

DMA_ITConfig(DMA2_Stream2, DMA_IT_TC , ENABLE);

DMA_ITConfig(DMA2_Stream5, DMA_IT_TC , ENABLE);

DMA_Cmd(DMA2_Stream2, ENABLE);

DMA_Cmd(DMA2_Stream5, DISABLE);

/* Enable SPI_MASTER DMA Tx request */

SPI_I2S_DMACmd(SPI1, SPI_I2S_DMAReq_Tx, ENABLE);

/* Enable SPI_MASTER DMA Rx request */

SPI_I2S_DMACmd(SPI1, SPI_I2S_DMAReq_Rx, ENABLE);

SPI_Cmd(SPI1, ENABLE);

}

void DMA2_Stream5_IRQHandler(void)

{

if(DMA_GetITStatus(DMA2_Stream5, DMA_IT_TCIF5) == SET)

{

DMA_ClearITPendingBit(DMA2_Stream5, DMA_IT_TCIF5);

}

}

void DMA2_Stream2_IRQHandler(void)

{

if(DMA_GetITStatus(DMA2_Stream2, DMA_IT_TCIF2) == SET)

{

DMA_ClearITPendingBit(DMA2_Stream2, DMA_IT_TCIF2);

DMA2_Stream5->NDTR = 15;

DMA_Cmd(DMA2_Stream5, ENABLE);

}

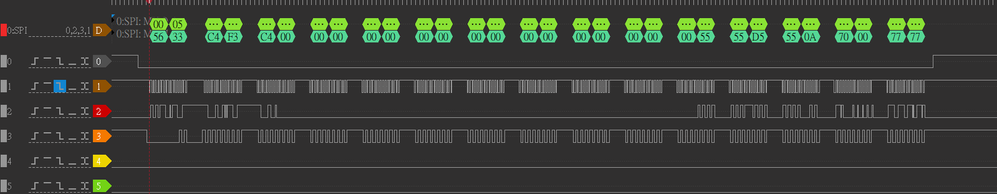

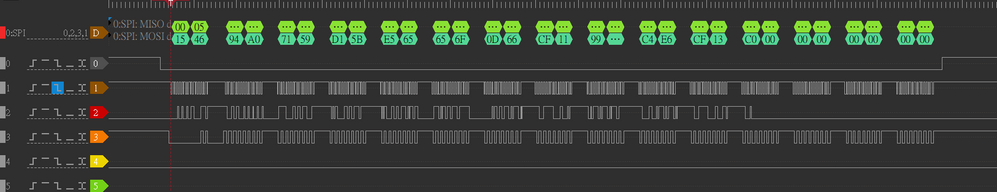

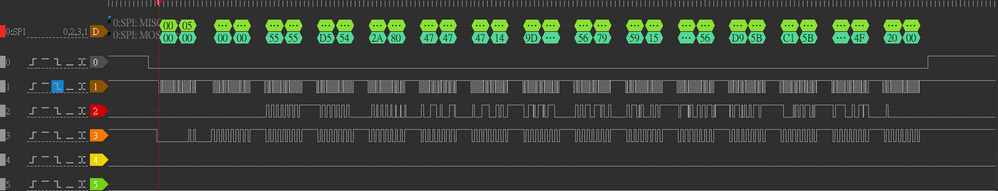

}Random capture by logic analyzer

- Labels:

-

DMA

-

SPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-17 2:30 AM

> GPIO_InitStruct.GPIO_Speed = GPIO_Speed_100MHz;

Use lower OSPEEDR setting, shorter interconnection, twist the SCK with a ground wire.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-20 2:05 AM

I try to twist the SCK with a ground wire, it can success communication in soft chip select.

But when I change the setting the MISO also shift in hard chip select.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-21 7:10 AM

Use lower OSPEEDR setting

- Time Drift Between 2 Identical Black Pill boards in STM32 MCUs Products

- Unable to do communciation between FDCAN and Classic CAN in STM32 MCUs Products

- STM32F401: UART 'Stop Bits' Setting in Others: STM32 MCUs related

- Can't transmit data with LoRa in STM32 MCUs Wireless

- STM32F429 + LAN8742A - reinitialize LWIP/network after ESD shock in STM32 MCUs Embedded software