- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F410 PLL Jitter on PWM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F410 PLL Jitter on PWM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-29 5:55 AM

Hello,

i want to use a really precise PWM signal but i get a lot of Jitter on it.

I am using the F410 with a 16Mhz crystal. The PLL produces from there a Frequency of 100Mhz (I need this high frequency for my other tasks).

The rest of my hardware needs one PWM signal with 1kHz and a 5ms on time. So i use a PWM Timer for that.

The problem now is, that the edges of this signal have a lot of jitter, around 3ns both on the on-time aswell on the period.

If i deactivate the PLL and directly use the 16MHz crystal for comparison, the jitter is much lower, around 0,5ns.

In the datasheed of the uC is a Table 44 about the Main PLL characteristics and in there is the Jitter with +-150ps much lower. As i see it, the chip has no option to add a external VCO-capacitor to the PLL.

Do anyone know, where this differences between datasheet and hardware come from and how can i fix this?

Best regards,

Philipp Diehl

- Labels:

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-05 12:47 AM

Hello @Sarra.S

those capacitors are not assembled. For my tests, i have used an signal generator Agilent 33220A and directly put the squarewave to the Pin PH0 (RCC_OSC_IN) and the HSE in BYPASS Clock Source mode.

I do not use the crystal here.

On my custom breadboard i have two 15pF with a 16MHz crystal.

Best regards,

Philipp

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-05 7:12 AM - edited 2023-09-05 7:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-05 7:42 AM

Hello @PDieh.1 ,

Yes, of course, I already prepared a code snippet based on your description to test the PWM jitter on both NUCLEO-F410 and NUCLEO-L433, but reproducing your same conditions will be optimal!

Meanwhile, I will also be testing Jitter on PLL with MCO output for both products, to isolate the source of the jitter, you may also want to test that!

You can email me your test code, and any other relevant test conditions!

Thank you!

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 1:13 AM

Hello @Sarra.S

sadly, i don't have your E-Mail, so i will attach the Files here.

I attached a 16MHz, 50% 3,3V squarwave signal to the PH0 Pin and the oszilloscope to PA3 on F410 and PA0 on L433.

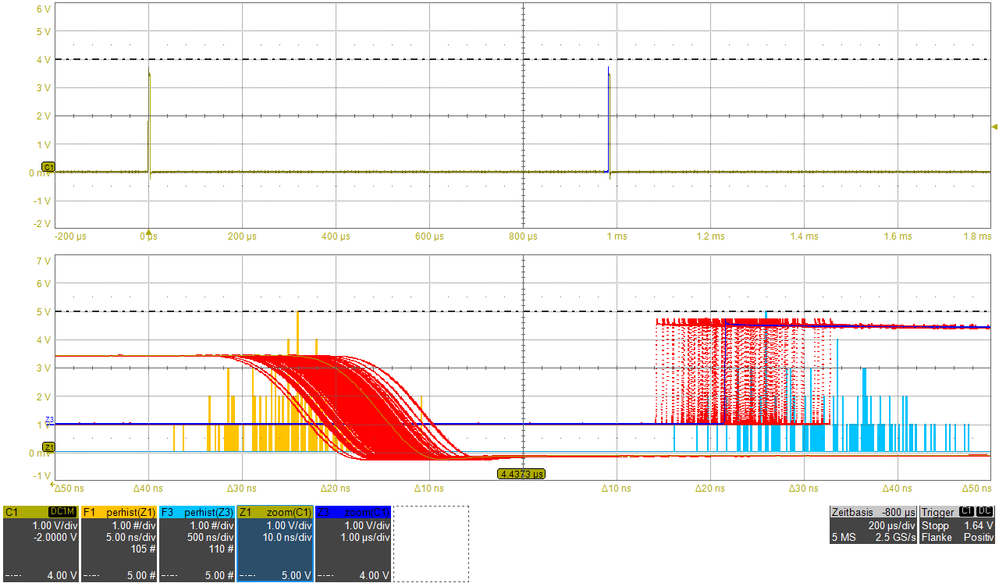

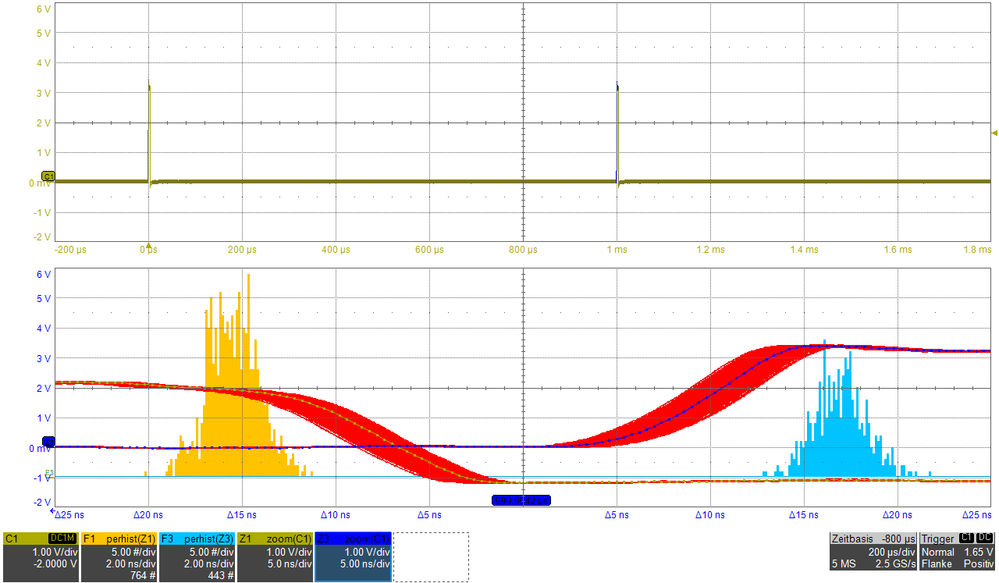

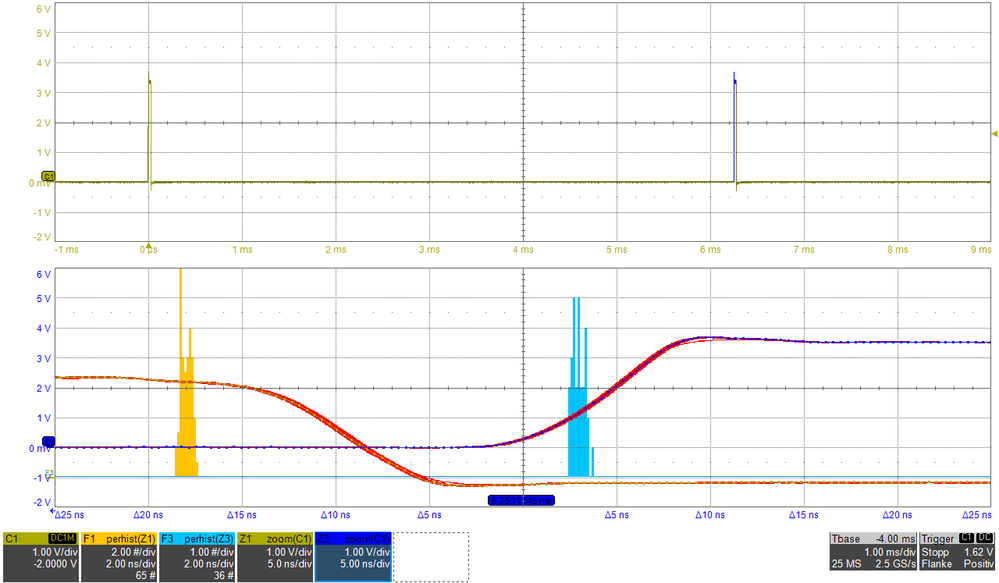

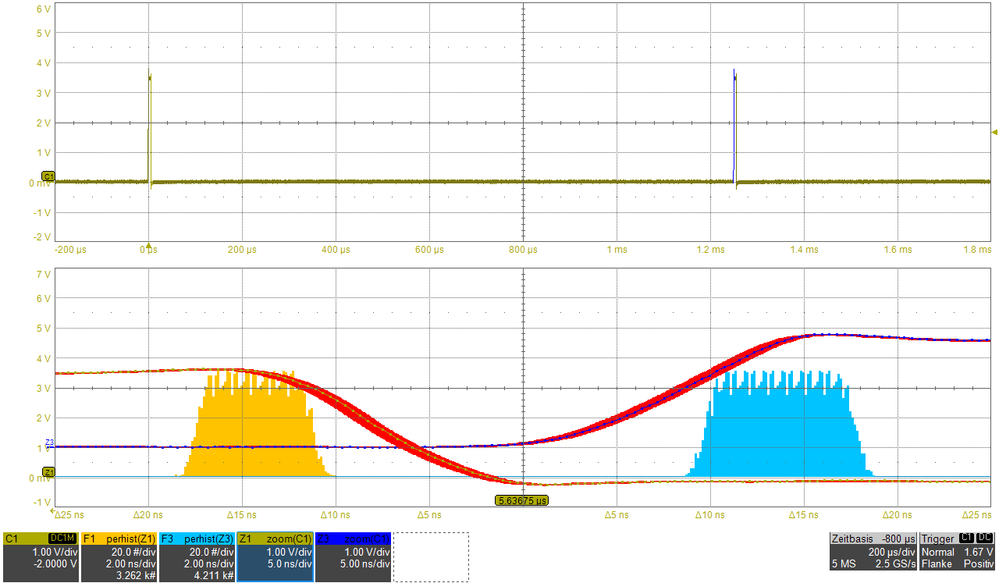

Here is what i meassured: (On the top is the PWM signal, on the bottom zoomed in there is in yellow on the left the first falling edge of the upper signal and in blue the next rising edge, both with persitence on)

F410 with internal Clock and PLL: Falling edge (yellow) Jitter ~20ns, rising edge ~1,5µs Jitter

F410 with external Clock and PLL: Falling edge (yellow) Jitter ~3ns, rising edge ~3,5ns Jitter

F410 with external Clock without PLL: Falling edge (yellow) Jitter ~0,5ns, rising edge ~0,5ns Jitter

L433 with internal Clock and PLL: Falling edge (yellow) Jitter ~6ns, rising edge ~1µs Jitter

L433 with external Clock and PLL: Falling edge (yellow) Jitter ~1ns, rising edge ~1ns Jitter

Is it correct, that the internal clock is that unprecise?

Do i have an error somewere?

I hope, this helps.

Best regards,

Philipp

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 1:37 AM

I think that it's a normal behavior with GPIO which 3ns jitter is very short to compare with 1KHz.

On my experience, the jitter can be appear with another device that had same ground and it also had high frequency.

So you should try to change your instrument which it had about 1Gsps, it can make 3ns jitter too.

I think you should find what is real problem.

Somehow every GPIOs is require a it load and almost of device's input need some base bias for their transistors so you should have a 50ohm or 100Ohm or some nearly value series with each GPIOs that was used and it also reduce a jitter level too.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 2:13 AM - edited 2023-09-06 7:06 AM

>Is it correct, that the internal clock is that unprecise?

yes. what can you expect from an r-c oszillator ? not much.... :)

and from my very limited tests (on I2S clock from pll on F411 ) i remember: STM cpu jitter was quite bad, just fulfilling the minimum required for "consumer audio" (even cheap ESP8266 was better)

afair it was about 300ppm .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 6:44 AM

You said "breadboard", that alone might be the cause for more jitter than expected.

Did you set the GPIOs to maximum output speed?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 10:31 PM

Hello @LCE

i call it breatboard, but in reality it is smaller than a nucle board and for most of the upper tests, i used a standard nucleo.

All GPIO are an minimum speed (00) for the tests, in my application only the pins for SPI are on max speed.

Best regards,

Philipp

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 10:50 PM

Okay, better stay with the Nucleo for these tests, unless your breadboard has a ground plane, short connection between crystal and MCU, good voltage decoupling, and so on...

Speaking of layout issues, there are some signal lines on the Nucleo which are absolutely terrible concerning routing, due to the fact that they are connected to (several) connectors.

So you might want to check the Nucleo layout files, maybe you got one of the worst signal lines.

I never used the F4, but with all my G4, F7 and H7 projects I always used the SAI / SPDIF TX for testing, always sourced by the internal PLL, with a 32 bit sine. Audio quality was always very good (>140dB SNR & THD, the limits of my SPDIF receiver CS8422), even with the clock input from the ST-link STM32.

The internal HSI / RC oscillator is completely unusable for almost anything related to signals.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 6:57 AM

Hello @Tinnagit

my oscilloscope is plugged in to a isolating transformer an besides the Signal Generator for the external clock, nothing else is connected to the nucleo.

I don't really get what you mean with the 1Gsps. My scope is at 2.5Gsps

I added a 100Ohm resistor between the Timer pin and ground but it had no effect on the jitter.

All it did was reducing the gradient between high/low.

Best regards,

Philipp

- STM32F410- VCAP voltage not generated, Unable to find the target through ST-Link in STM32 MCUs Products

- Trigger ADC by TRGO in STM32 MCUs Products

- STM32U585 CLOCK JITTER in STM32 MCUs Products

- May I ask how to modify this code to replace the HAL_GPIO_EXTI_Callback () callback function? in STM32 MCUs Embedded software

- STSPIN32G4 PWM Output Jitter in STM32 MCUs Motor control