- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F407 with a 50.0MHz Oscillator

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F407 with a 50.0MHz Oscillator

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-20 11:00 AM

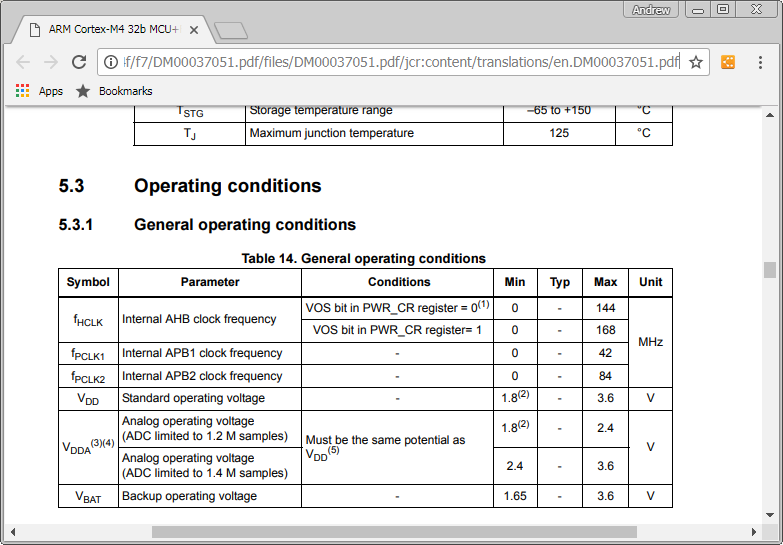

I am running an STM32F407 with an ECS-2033-500BN Oscillator (50.0MHz) to accommodate the MCU and the ETH off the same oscillator. The circuit uses a fanout buffer to distribute the clock. Nowhere can I find information on how to configure the STM32F4 system clock with this high of a value (I assume there's a divide by 2 enabled in the bowels of the MCU) and the Clock Configuration tool doesn't help. Any suggestions? And yes, I've looked through the forum and the datasheet and I haven't been able to get the circuit to run.

I know the circuit works because previous FW was developed using NuTTx. I am porting the code to IAR and am stuck at the PLL initialization in the generated file system_stm32f4xx.c at the line:

/* Wait till the main PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0) { }Any help would be greatly appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 12:13 AM

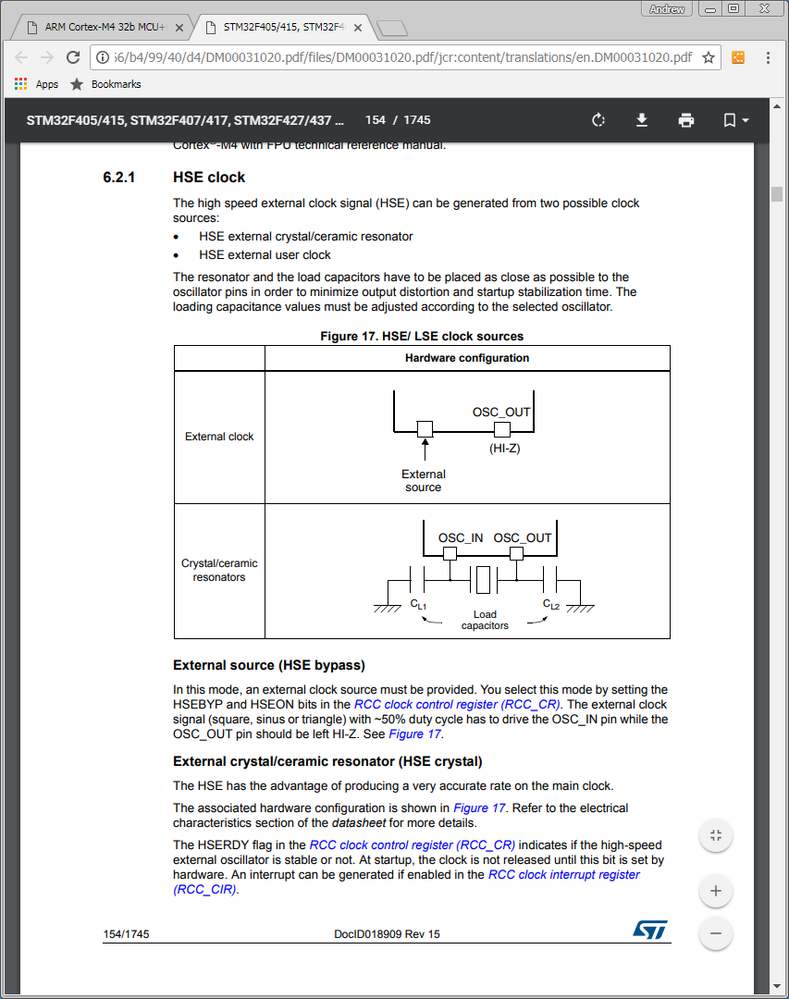

With external clock source you should set HSE to BYPASS.

To which pin is the clock connected?

You can check it with outputting HSE to MCO pin.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 12:49 AM

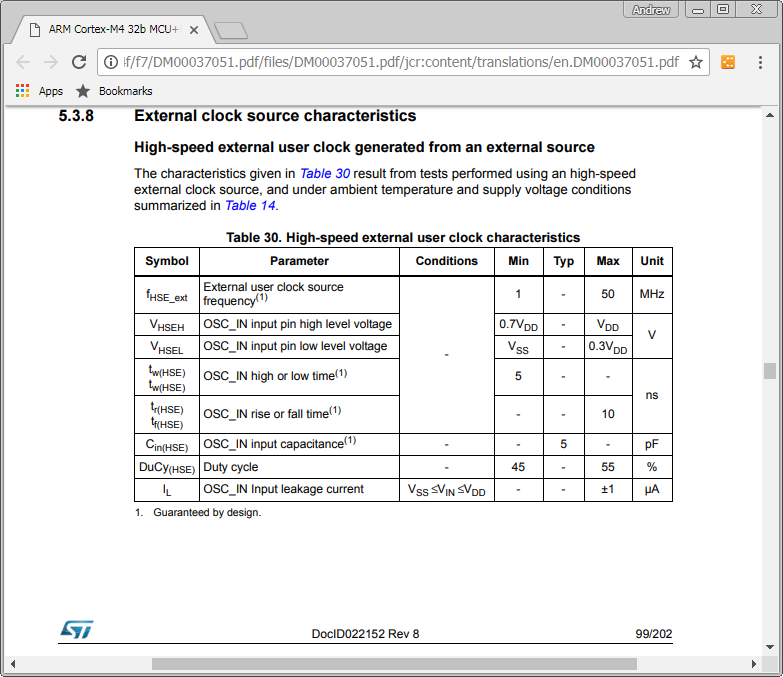

50 MHz seems a bit high - officially (DS) only quartz frequencies from 4.0 MHz to 24.0 MHz are supported.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 5:13 AM

'

Nowhere can I find information on how to configure the STM32F4 system clock with this high of a value...'

you mean the datasheet says nothing about that? seems to be a major flaw,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 6:33 AM

Actually 50MHz is allowed - it is the max:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 6:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 7:04 AM

Yes, AvaTar, that's what tripped me up as well. Also, the Clock Configuration tool does not allow 50 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 7:15 AM

Thank you, Andrew, for the reply. The datasheet, DM00037051.pdf, mentions the 50 MHz OSC in Figure 98, but doesn't really provide any more information. The reference manual, en.DM00031020.pdf, is what I was missing. However, other than the bypass, it doesn't provide the same level of detail as the Clock Configuration tool.

Once the bypass is selected and HSE is on, how does the /2 get selected? From the block diagram, either /2 or /20 is possible. And, once this is setup, can the HSE be treated as 25MHz in order to set the other parameters? I.e. PLL_N, PLL_Q, PLL_M, etc?

Thank you for all the help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 7:35 AM

I didn't check the datasheet in detail, just relied on the 'front page information' - my bad ...

Also, the Clock Configuration tool does not allow 50 MHz.

Guess you mean the Excel tool, never used it myself.

I either used the output of this tool, delivered with the (SPL) project directly, or adjusted the clk configuration code (clk source, frequency and especially PLL multipliers).

The emitted source code (system_stm32f40x.c and *.h) had pretty decent comments, never had to consult the RM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-21 7:46 AM

ST - like many (most?) others - split the description of their products across two documents:

- The Datasheet - covers physical parameters; electrical, timing, mechanical specifications, etc

- The Reference Manual - covers operation of the various parts, registers, etc

- STm32f407: Which Registers control HSI or HSE oscillator selection and PLL clock source? in STM32 MCUs Products

- RTC oscillator STM32F407 in STM32 MCUs Products

- STM32F407ZGT7 reset when write to SPI1 DR in STM32 MCUs Products

- STM32F407 SDIO CLK line is running below 400 kHz in STM32 MCUs Products

- Does HSE timeout period affects Bootloader booting time if external oscillator is used? in STM32 MCUs Embedded software