- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F4 synchronise timer + generate variable ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F4 synchronise timer + generate variable frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-07 3:56 AM

Hi,

I have a litte problem. I need to generate avariable frequency

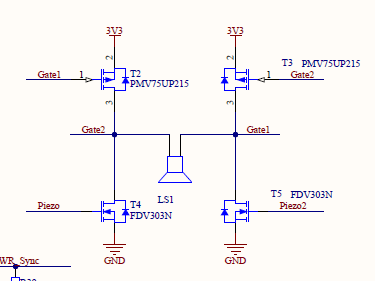

(not duty cycle) for a piezo buzzer. Unfortunately the PCB layout is givn as a H-bridge (see image). ''Piezo'' is connected to TIM4_CH1 and ''Piezo2'' is connected to TIM3_CH1. Since the PCB does not use the pins of a advanced timer I can not use the built in TIMx_CHx_N feature / dead time generation. So I thought I could try to synchronise the two timers TIM3 and TIM4 and generate a variable frequency with 50% duty cycle. But I could not find any code showing the generation of a variable frequency (variable prescaler, reload value ???) synchronising twoinverted

timers. Can anyone help me with a piece of code, a link or other sources than the reference manual? Thank you in advance #timer-synchronize-frequency

#timer-synchronize-frequency

- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-07 12:21 PM

Can't you impart the desired phase relationship using the CNT registers of each timer?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-03-13 10:45 PM

I’m not even going to think about suggesting how you might go about doing this in the HAL, but I may be able to help with register-level operation.

Sorry, but you’ll be using the reference manual.

If you have a look in v11 of the F4xx reference manual, in section 18.4.3 TIMx slave mode control register, on p623 you’ll find that it’s possible to slave TIM3 to TIM4, or TIM4 to TIM3 – vital for your requirement.

It doesn’t matter which is master and which is slave, because they have identical functionality.

If you run the master in Reset mode (TIMx->CR2.MMS = 000b) and slave in Reset mode (TIMx->SMCR.SMS = 100b), then after either the master wraps or you manually generate an update event (EGR register, UG flag) both timers will be synchronised, and will stay synchronised as long as the slave has a period (set with PSC and ARR registers) >= than the master’s.

I’d set the slave’s PSC to match the master’s, and the slave’s ARR to maximum; then the master almost entirely controls the slave’s behaviour.

Then it’s just a case of getting OC1 working on both timers (master in PWM mode 1, slave in PWM mode 2, i.e. inverted – see CCMR1 register), and setting the CCR1 registers of both timers to the same value, i.e. 50% of ARR.

To change the frequency, wait for the master to interrupt/wrap, then change master ARR, master CCR1 and slave CCR1 and manually generate an update event.

This will cause a small aberration in the frequency for the first cycle (only) of the new frequency, which for the purpose of driving a piezo is probably irrelevant.

- ADC in DMA circular mode with LL Library Problems in STM32 MCUs Embedded software

- STM32F407VG sometimes reads one additional Timer overflow. in STM32 MCUs Products

- About PWR activation when setting clock in STM32 MCUs Products

- SWV Timeline error -500000000 in STM32CubeIDE (MCUs)

- ADC Calibration Return Fails due to ADC_CALIBRATION_TIMEOUT on STM32G030X6 in STM32 MCUs Embedded software