STM32 HRTIM BURST DMA CONFIGURATION

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-13 12:54 AM

Hi all,

I am trying to configure burst dma on my board (stm32g474). I have successfully configure the dma for single register, however, when I want to configure dma for more than one register, I failed to do that as it only allow me to fill one address for DMA Src address when 2 channels should be updated. Do anyone know how should I configure the DMA Src address if I want to use dma to update 2 respective dma channel?

- Labels:

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-13 2:45 AM

Hello @OFN

If I understand correctly the question, you need to increment source and destination address by the number of data items (already in CNDTR before being decremented) to the second DMA channel. Then, you can configure the parameters and enable the second DMA channel.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-22 8:07 AM - edited 2023-12-01 4:49 AM

Let me share with you some additional information!

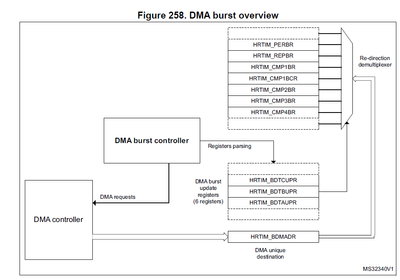

Here the Figure 258. from RM0440 on HRTIM chapter (especially 27.3.23).

On the overview below, there are 3 types of registers :

- HRTIM_BDMADR (Burst DMA data register) : DMA unique destination (burst operation is started by the first write access in this register)

- Registers to update for your application (eg : HRTIM_PERBR, HRTIM_CMP1BR....)

- 6 update registers multiplexing HRTIM_BDMADR to the register you want to update. (HRTIM handles internally the data re-routing to the final destination register).

It is only necessary to have the DMA controller pointing to the HRTIM_BDMADR register as

the destination, in the memory, to the peripheral configuration with the peripheral increment

mode disabled.

Once you write in HRTIM_BDMADR, it's automatically triggers (no need Burst DMA source):

- The copy of the data value into the registers enabled in BDTxUPR and BDMUPR register

bits - The increment of the register pointer to the next location to be filled

Best Regards,

Pierre

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.