- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32 H7 - I2S Clock Timing Problems (runs at 1.02...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 H7 - I2S Clock Timing Problems (runs at 1.027 Mhz for some reason) - See PulseView

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-30 12:41 PM - edited 2023-10-30 12:43 PM

Hello,

Still trying to get I2S working on the H7...

Opened up PulseView to check the clock between another connected device...

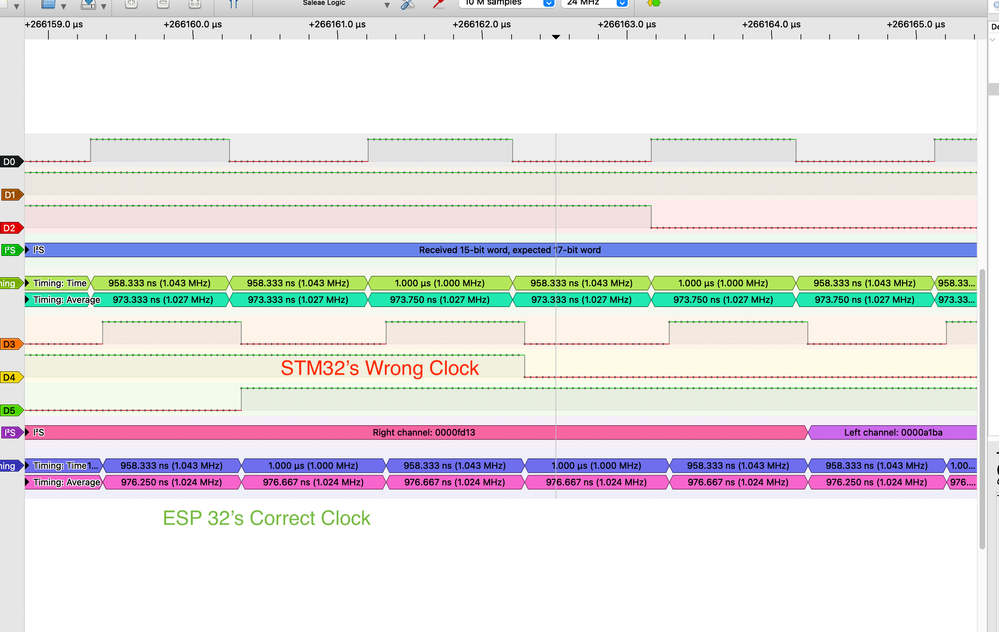

Much to my surprise, the STM32 is actually outputting 1.027 Mhz average clock pulses instead of the ESP32's 1.024 Mhz.

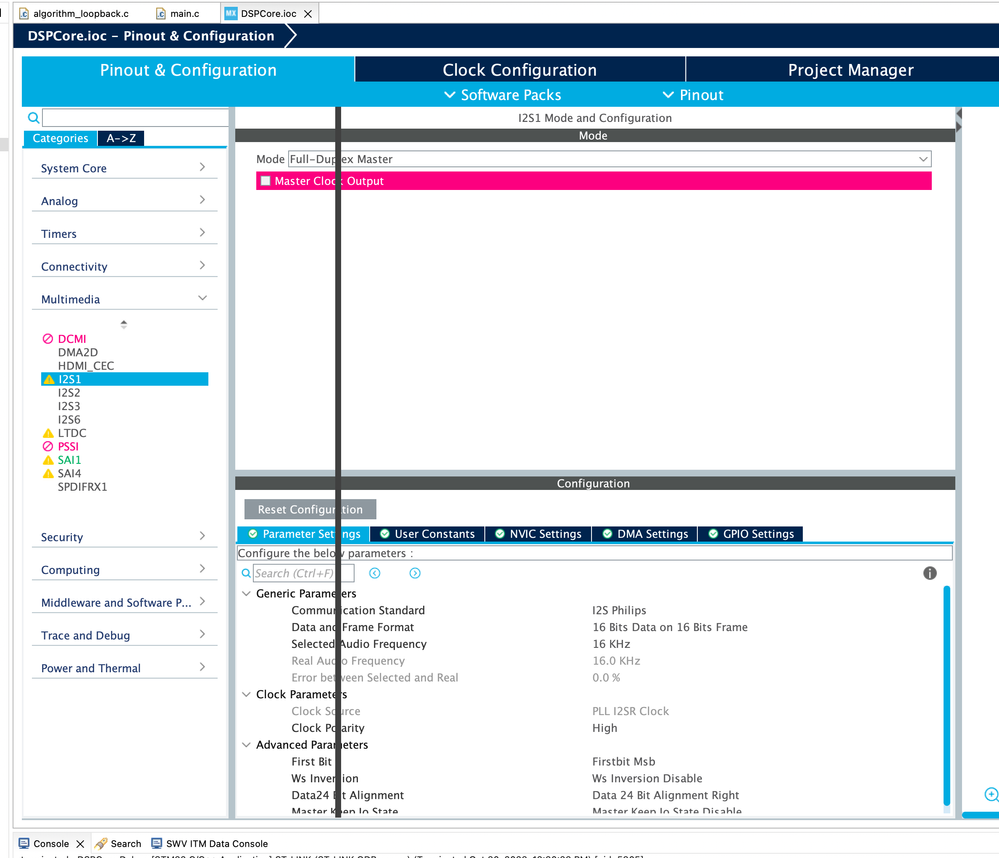

Checked the Clock in STM MX, shows 0% error and an input clock of 2.048 Mhz which is divisible. Tried also 20.48 Mhz with no change. There appears to be no divider settings. Any reason for this wrong output clock?

There are many "Expected 16 bit word, received 17 bit" etc, with varying bits because of the wrong clock. Expected is 16 bits.

Solved! Go to Solution.

- Labels:

-

Bug-report

-

I2S

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-31 5:54 PM

The targeted 16 kHz sample rate in the screenshots points to this solution not requiring a Hi-Fi audio. Anyway I would avoid using PLL in fractional mode unless actually necessary. I the latest screenshots the author has already found the best rational fraction for PLL, which deviates from the ideal frequency by +11 ppm. Humans can detect a pitch variation of 0,3 % (3000 ppm) at best. And that is for a variation, not a constant offset! In other words - there is absolutely no point in using a fractional PLL mode and increasing the jitter unnecessarily.

- « Previous

-

- 1

- 2

- Next »

- Can't program/connect to STM32U031K4U6 over SWD in STM32 MCUs Products

- STM32U5 UART: Unexpected Dependency on HAL_HalfDuplex API for RS485 Operation in STM32 MCUs Products

- STM32H750 and USB3300-EZK Startup Issue in STM32 MCUs Products

- Error in initializing ST-LINK device. Reason: Target not halted. in STM32 MCUs Boards and hardware tools

- NUCLEO-N657X0-Q unable to upload code in STM32CubeIDE (MCUs)