- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- SAI FS configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SAI FS configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-17 7:24 PM

Hi,

I have a design that uses a STM32H757 with an external ADC that streams data out to the SAI peripheral. The ADC is the bus master and generates the clock. The ADC data is the PCM / DSP protocol format.

I setup my SAI with the free protocol configuration and configured the channel parameters. The channel parameters are:

- 32 bits per channel

- 4 channels per frame

- 128 bits per frame

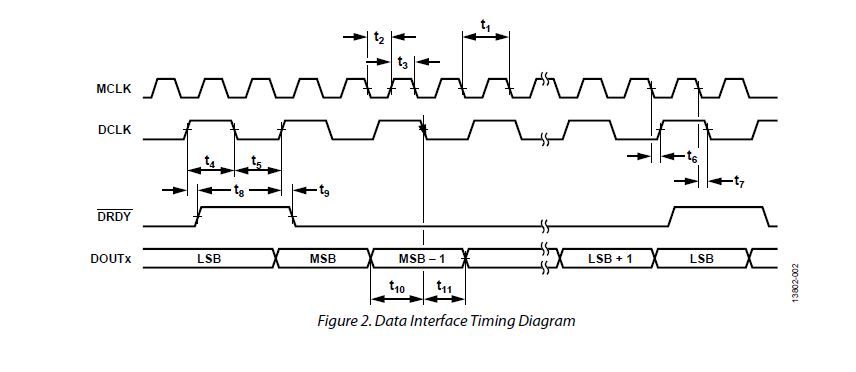

I am running into issues when configuring the Frame register. The ADC documentation has the following diagram:

The falling edge of the DRDY signal indicates that new data is available and will be output on the data lines.

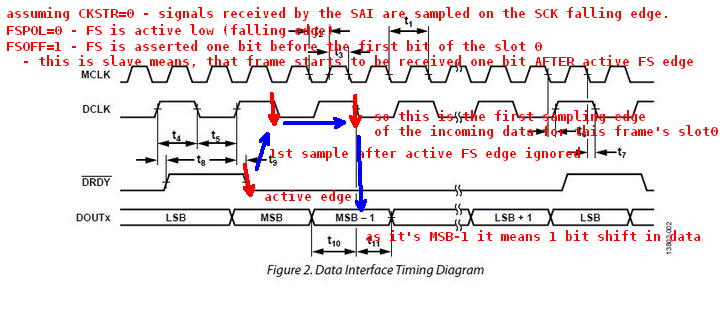

My confusion is in the reference manual of the STM32H757. According to the register description the FSPOL register value should be set to 0 for a falling edge FS, FSOFF value should be set to 1 because the FS signal is asserted before the first bit of the frame. This configuration does not work as expected and the data is left shifted by 1 bit. According to this ST Document the FSPOL behaves in the opposite manner.

What should be the correct SAI_xFRCR register configuration for the diagram above?

Thank you!

- Labels:

-

SAI

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-18 4:43 PM

To me, it works as expected:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-18 6:59 PM

Thanks for the quick response!

I tried that configuration and seems to work as expected. Does this mean that I would have to set the FSALL register to 0 (for 1 active clock clock)?

Also, I keep getting Late Frame Synchronization Detection (LFSDET), does this point to a bad configuration?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-19 2:07 AM

The SAI chapter is not very concisely written, and especially the slave working is rather neglected, both in narrative and in the description of the registers .

I believe, in slave mode, only the FSPOL-determined edge of the FS signal is detected, and its length is ignored (that's what that picture from the presentation you are referring to is supposed to show, by "[the other] edge is ignored). In other words, IMO, FSALL content in slave mode is ignored.

LFSDET indicates, that there were more clocks between successive active FS edges than set in xFRCR.FRL.

One possible way to test your settings might be to turn the SAI to master (without the slave connected, e.g. on a Nucleo-style devboard, not necessarily 'H7x7 as the SAI module will be pretty similar across all STM32 modes which include it) and try to transmit frames with the same settings, the waveforms should then be similar to what in the reversed setup the master sends.

JW

- USBPD Library Never sends PS_RDY in STM32 MCUs Embedded software

- B-G431-ESC1 Hall sensors connection issue in STM32 MCUs Boards and hardware tools

- SPI Comminication between two microcontrollers in STM32 MCUs Embedded software

- STM32H753ZI / MDMA issue with linked list (DMA ADC) in STM32 MCUs Embedded software

- STM32C092GCU6: FDCAN interrupt handler name mismatch in STM32CubeMX (MCUs)