- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Resetable DMA for predefind amount of transfers

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Resetable DMA for predefind amount of transfers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 11:49 AM

Hey everyone,

I've got a small issue.

I've got a Dma that fills a buffer(Double buffer so 2 actually) with data at every rising clock edge. I only want this clock to trigger the DMA 192 times until a reset signal is received. Once the reset signal is received, the DMA should just carry on where it left off, so position 193 of the buffer.

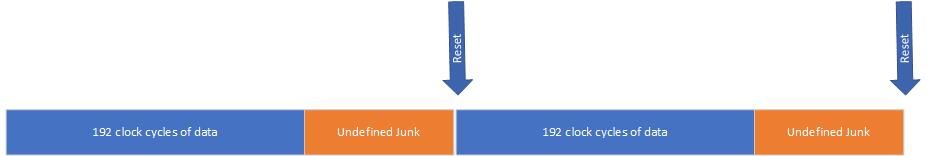

This image tries to portray what Im trying to do. I have 192 cycles of data, followed by junk until the reset signal is received.So I want the Timer to trigger the dma for 192 rising edges, stop and wait for reset and then repeat.

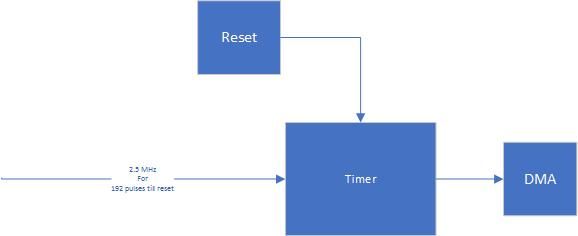

Essentially this is what my timer configuration is like. An input capture which triggers the dma every rising edge and then a slave mode set for reset.

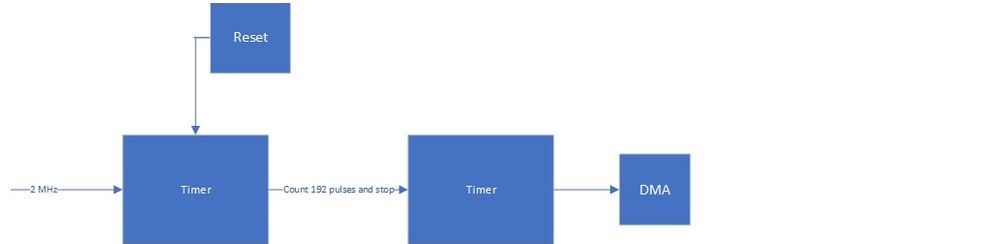

If I cant do this directly on the timer, is there a way that I could cascade two timers, where the timer would come in between the 2.5 MHZ signal and the timer that triggers the dma, pass through the clock signal and stop once 192 pulses have been received and restart on reset.Something like this:

I've tried a few implementations with cascaded timers and gated mode, but due to the gated mode not resetting the counter it doesn't seem to help. I've also found nothing on the forum but seen a few similar questions.

Thanks in advance for any help.

Not sure if I'm missing something obvious >.<

dma-transfer nucleo input-capture-mode stm32f7Solved! Go to Solution.

- Labels:

-

DMA

-

STM32F7 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 12:49 PM

Perhaps TIM1/TIM8, one shot, with a repetition count? ADC triggering from CCx

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 12:49 PM

Perhaps TIM1/TIM8, one shot, with a repetition count? ADC triggering from CCx

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 02:51 PM

Hi Clive,

thank you for the response.

I'm a little lost but think I have an idea of what you mean.

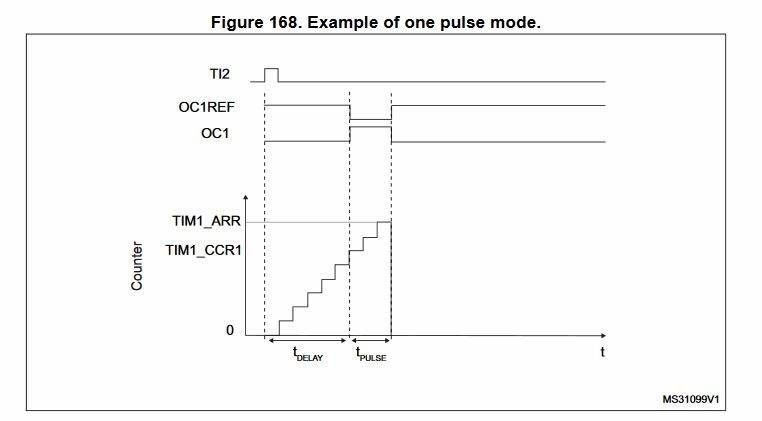

My understanding: one pulse mode would produce a pulse with a user fixed length and a repetition counter would produce N amount of pulses.

I think your referring to the following :

And looking at the reference manual:

I'd need to set the pulse length to 1 so it starts on the rising edge and stops on the falling edge of the input signal. The delay to 0 as I want no delay between the input and output pulse (Also enable fastmode by setting OCxFE).

I can't find much on the repetition counter for this mode, but I'm assuming it would produce 192 pulses at the output for 192 pulses at the input and then stop. Once the reset signal is received this process would restart?

Thank you for all the help thus far!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 05:00 PM

Is DMA pulling data from GPIO or ADC?

Repetition mode has the count cycle N times (CNT=0..ARR,0..ARR, etc), there will be 1 Update event and N CCx events

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-10 05:35 PM

It's pulling from GPIO, so 192 rising edges from the 2.5 MHz signal should result in 192 samples read from GPIO to memory by the Dma and then nothing should be read till the reset signal arrives. Then it should repeat the 192 read.

- Hello, i try to use the SPI interface on STM32f3 DISCOVERYBOARD. My problem is that my clock toggles, even though the data transfer is complete. The busy flag is not yet reset either. What can that be? Ther is an Osziplot wich shows the Problem in STM32 MCUs Products

- Reset ''shadow M0AR'' DMA-controller register after incomplete DMA-transfer? in STM32 MCUs Products