- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Minimum Frequency for Bypass mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Minimum Frequency for Bypass mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-23 05:55 PM - last edited on 2023-11-23 10:14 PM by STTwo-32

Hello Community,

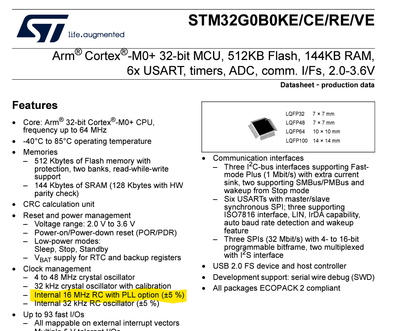

I am working on a use case where I have 4 remote MCUs that ideally should be synced with a host MCU. I however have no way to even install an external precision Clock source on these remote MCU's (due to various environmental & budget limitations), while I can accept a precision reference clock signal from any external device that is off-board ie of PCB via one available differential channel on my CAT6e cables. I wish to seek your insights to confirm my assumptions & clear my doubts if I can use this external Clock source to clock the HSE & replace the lower +-5% stability internal 16Mhz HSI on STM32G0B0 MCUs.

Point #1:

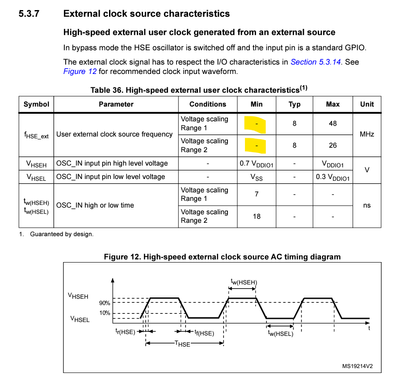

The Datasheet does NOT mention any minimum frequency for the external clock signal to HSE as input clock refernce, so in theory (for sake to my understanding) does this mean I can use a signal as low as 32Khz for driving the MCU? Or am I missing something obvious here?

Then in theory, can I also use a stable 50/60Hz signal that is available to clock the MCU?

Point #2:

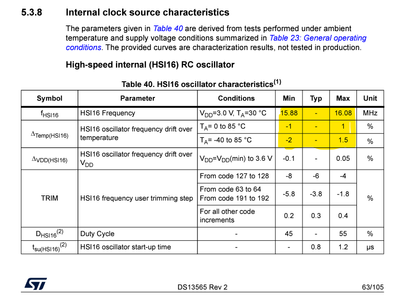

Further I am confused, as the Datsheet of the STM32G0B0RET6 mentions the HSI16 has +-5% stability on the first page, while the internal page on clock charectiristics mentions it has ~1.25% stability

I am confused, is this a major typo in the datasheet or am I missing something here?

Your insights shall be appreciated.

Solved! Go to Solution.

- Labels:

-

STM32G0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-23 08:23 PM

1) No minimum, correct. But note that PLL has minimums which will give you a restriction if you use PLL for anything. Note that 50/60 Hz mains frequency is not particularly accurate either.

The reference manual will give you more information. The PLL restrictions are listed there.

2) Seems like a typo to me. The "features" section is less accurate in general in my experience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-23 08:23 PM

1) No minimum, correct. But note that PLL has minimums which will give you a restriction if you use PLL for anything. Note that 50/60 Hz mains frequency is not particularly accurate either.

The reference manual will give you more information. The PLL restrictions are listed there.

2) Seems like a typo to me. The "features" section is less accurate in general in my experience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-23 10:46 PM

Hello @Chubs

thank you for your request. I will check this internally and come back to you as soon as possible.

Best Regards.

STTwo-32

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-24 09:30 AM

Hi again @Chubs

Thank you for having reported this issue.

An internal ticket (number: 167147) is submitted to escalate this issue internally for check and analysis.

(PS: number 167147 is an internal tracking number and not available outside of ST).

Best Regards.

STTwo-32

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-24 10:34 AM

CMOS, should clock to DC, wants 50/50 duty, VCO frequencies, dividers, and comparison frequency should limit viable rates for PLL

Most power distribution these days is monitored by GPS

Up vote any posts that you find helpful, it shows what's working..