- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Maximum external clock frequency for STM32H5 t...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Maximum external clock frequency for STM32H5 timers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 11:54 AM

What is the maximum clock source frequency can I use as an external clock for timer?

I have a 20MHz source and PLL frequency made out of this source. The purpose - generate lower frequency pulses that synchronous to that 20MHz clock with controlled delay. I can get 100MHz, 120MHz, 140Mhz, 160 MHz out of that PLL for delay of less or more precision and would like to know what will I be able to get.

It could be easy made with FPGA, but since ST got such high speed MCU, I hope I can do it just with a MCU. MCU will be needed anyway.

Solved! Go to Solution.

- Labels:

-

STM32H5 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 12:17 PM

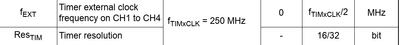

from H563 ds:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 12:17 PM

from H563 ds:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 12:30 PM - edited 2023-11-17 12:31 PM

I see, 125MHz, than.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-17 12:55 PM

But the TIM's on the STM32 aren't very flexible / functional at all.

Integer dividers, single counting element, 4 channels. Saturated by interrupts into the few hundred KHz

Ok for generating 4x 50 Hz Servo signals.

I'd imagine you could do something a lot better with a CPLD, and perhaps an adder circuit instead of a counter. ie simple phase adder for NCO / DDS

There is a clock domain synchronizer on the front end to get the input clock into the 150 MHz domain

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-20 10:35 AM - edited 2023-11-20 11:12 AM

Played last Friday. With 100MHz for the beginning.

The main problem for my task - the trigger can't have a shorter period than the counting timer. I mean, if I use a PWM or one pulse output, for example, the trigger signal should come, at least, right after the pulse finished. Better with some delay after the pulse.

That means I have to use FPGA. CPLD like Altera MAX V would be great for my task, but Intel still have problems with its production, Xilinx/AMD does not have modern CPLDs. Tried to look into Lattice - small ones won't work for me, big ones are not much cheaper than small Spartan 7. And I never worked with Lattice yet.

- OPENAMP STM32H745 memory problems in STM32 MCUs Embedded software

- STM32H7 optimized SPI driver for use in DMA mode in STM32 MCUs Products

- How to disable XSPI SCK Clock preamble? in STM32 MCUs Products

- HSE Clock for CAN in STM32 MCUs Products

- STM32H523 QUADSPI W25Q64 External Loader in STM32 MCUs Products